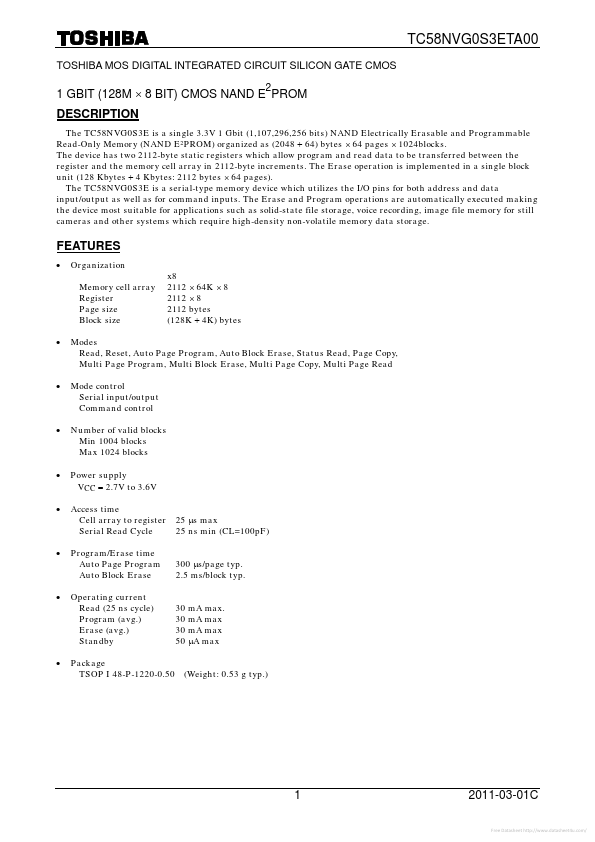

TC58NVG0S3ETA00

Overview

- Organization Memory cell array Register Page size Block size

- x8 2112 × 64K × 8 2112 × 8 2112 bytes (128K + 4K) bytes Modes Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read Mode control Serial input/output Command control Number of valid blocks Min 1004 blocks Max 1024 blocks Power supply VCC = 2.7V to 3.6V Access time Cell array to register Serial Read Cycle Program/Erase time Auto Page Program Auto Block Erase Operating current Read (25 ns cycle) Program (avg.) Erase (avg.) Standby 25 µs max 25 ns min (CL=100pF) 300 µs/page typ. 2.5 ms/block typ. 30 mA max. 30 mA max 30 mA max 50 µA max * * * * * *

- Package TSOP I 48-P-1220-0.50 (Weight: 0.53 g typ.) 1