TC74VHC161FN

TC74VHC161FN is SYNCHROMOUS PRESETTABLE 4-BIT COUNTER manufactured by Toshiba.

- Part of the TC74VHC161 comparator family.

- Part of the TC74VHC161 comparator family.

Features

- High speed: fmax = 185 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 µA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Power down protection is provided on all inputs.

- Balanced propagation delays: tp LH ∼- tp HL

- Wide operating voltage range: VCC (opr) = 2 to 5.5 V

- Low noise: VOLP = 0.8 V (max)

- Pin and function patible with 74ALS161/163

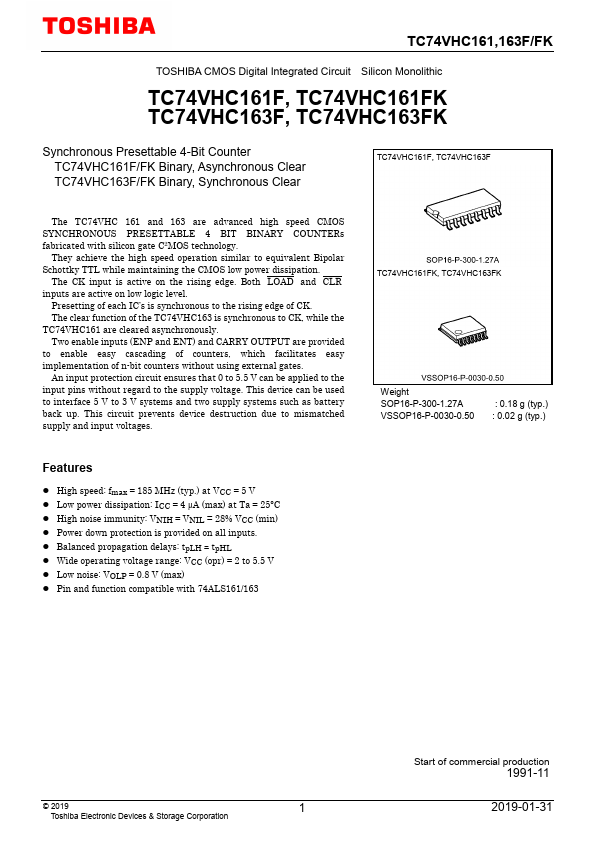

TC74VHC161FN, TC74VHC163FN

TC74VHC161FT, TC74VHC163FT

Weight SOP16-P-300-1.27A SOP16-P-300-1.27 SOL16-P-150-1.27 TSSOP16-P-0044-0.65A

: 0.18 g (typ.) : 0.18 g (typ.) : 0.13 g (typ.) : 0.06 g (typ.)

1 2006-02-01

Pin Assignment

TC74VHC161,163F/FN/FT

CLR 1 CK 2 A3 B4 C5 D6

ENP 7 GND 8

(top view)

IEC Logic Symbol

16 VCC 15 CARRY OUTPUT 14 QA 13 QB 12 QC 11 QD 10 ENT 9 LOAD

CLR LOAD

(1) (9)

ENT ENP

(10) (7) (2)

TC74VHC161 CTRDIV 16

CT = 0 M1 M2 G3 3CT = 15 G4

C5/2, 3, 4+

A (3) 1, 5D [1]

B (4)

[2]

C (5)

[4]

D (6)

[8]

(15) CARRY OUTPUT (14) QA (13) QB (12) QC (11) QD

CLR LOAD

(1) (9)

ENT...