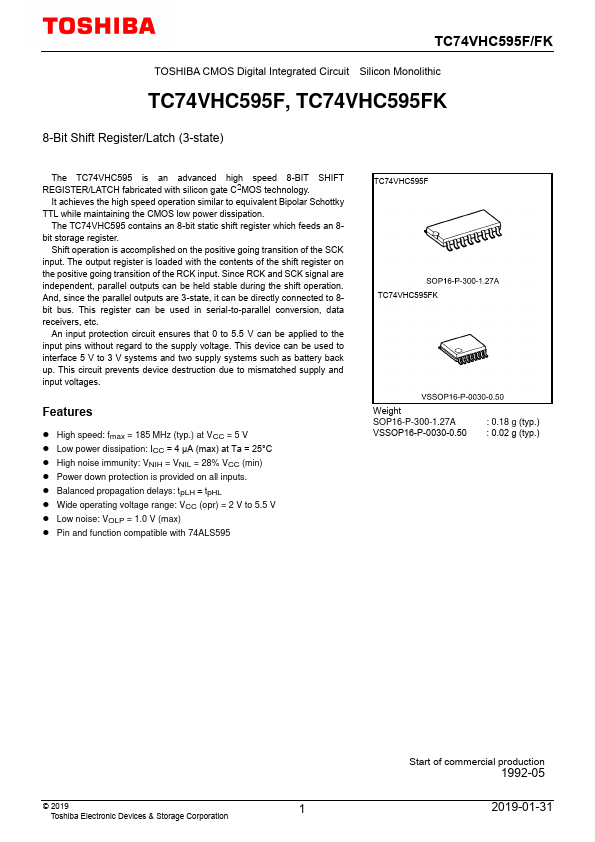

TC74VHC595F Description

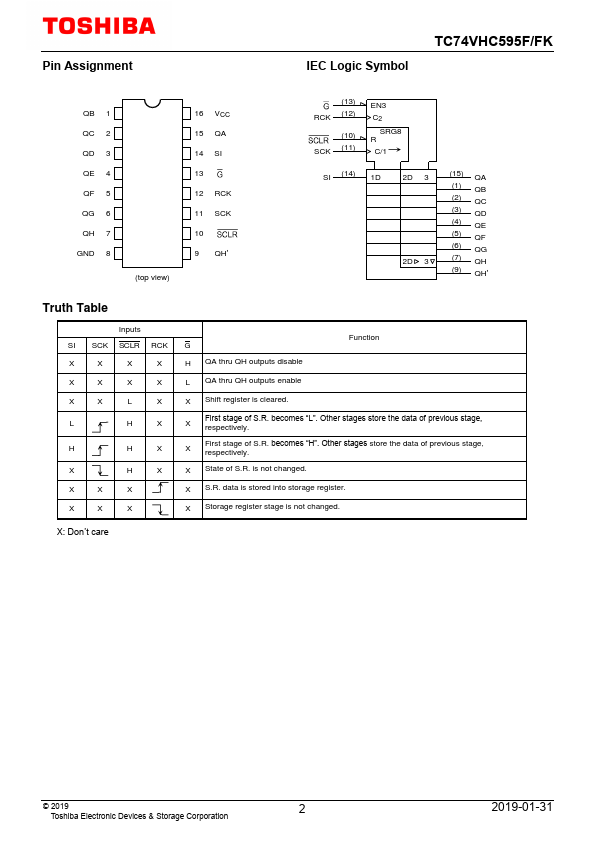

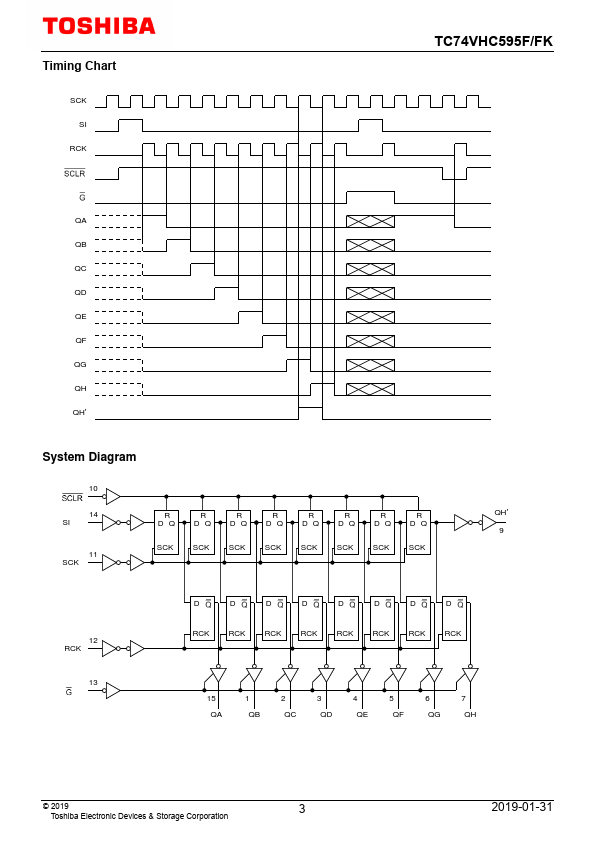

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation. The TC74VHC595 contains an 8-bit static shift register which feeds an 8bit storage register. Shift operation is acplished on the positive going transition of the SCK input.

TC74VHC595F Key Features

- High speed: fmax = 185 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Power down protection is provided on all inputs

- Balanced propagation delays: tpLH tpHL

- Wide operating voltage range: VCC (opr) = 2 V to 5.5 V

- Low noise: VOLP = 1.0 V (max)

- Pin and function patible with 74ALS595