TC74VHC74FT Overview

Key Specifications

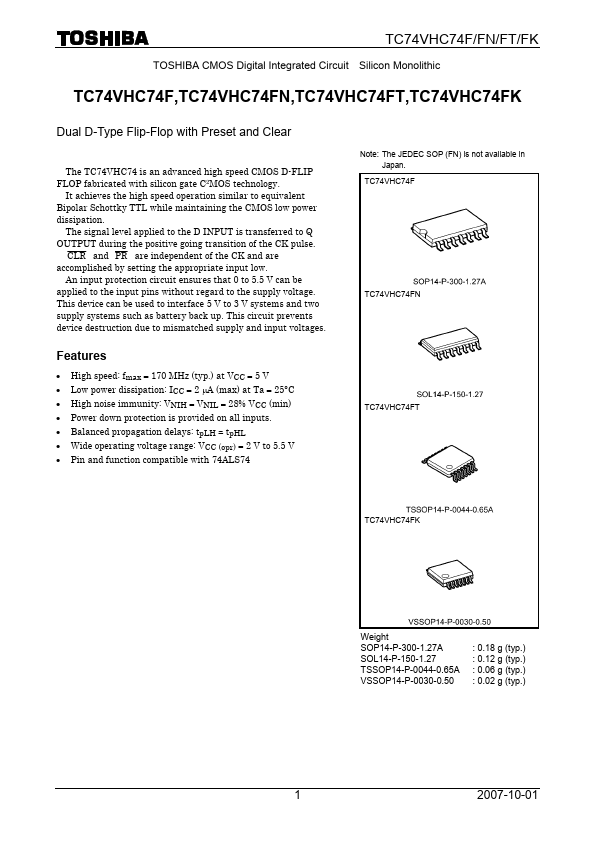

Package: TSSOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 5 V

Key Features

- High speed: fmax = 170 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 2 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Power down protection is provided on all inputs

- Balanced propagation delays: tpLH ∼- tpHL