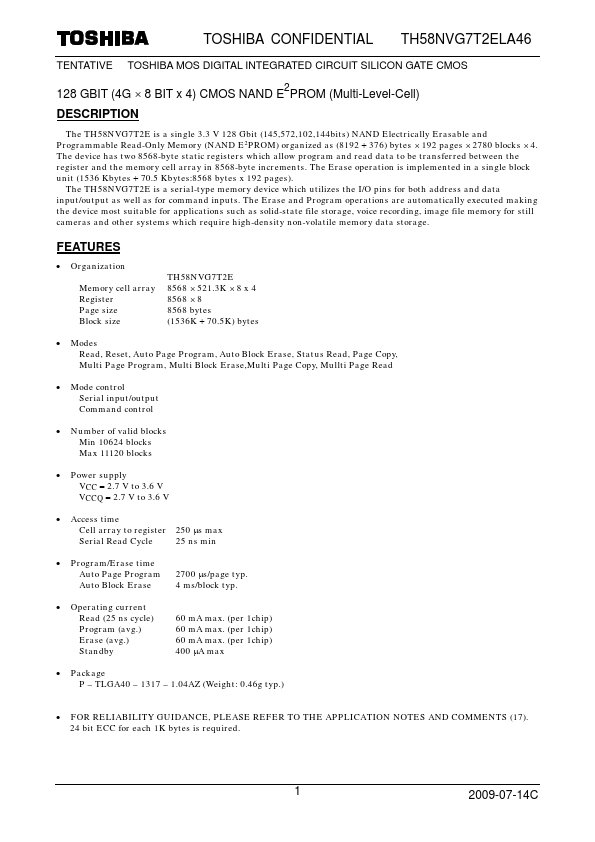

TH58NVG7T2ELA46

Description

The TH58NVG7T2E is a single 3.3 V 128 Gbit (145,572,102,144bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as (8192 + 376) bytes × 192 pages × 2780 blocks × 4.

Key Features

- Number of valid blocks Min 10624 blocks Max 11120 blocks

- Power supply VCC = 2.7 V to 3.6 V VCCQ = 2.7 V to 3.6 V

- Access time Cell array to register 250 µs max Serial Read Cycle 25 ns min

- Program/Erase time Auto Page Program Auto Block Erase 2700 µs/page typ. 4 ms/block typ

- Package P - TLGA40 - 1317 - 1.04AZ (Weight: 0.46g typ.)