TMP4321AP

TMP4321AP is single chip microcomputer manufactured by Toshiba.

- INTEGRATEDCIRCUIT iii :.: TECHNICAL DATA

TOSHIBA MOS Digital Integrated Circuit Silicon Monolithic

N-channel Silicon Gate Depression Load

GENERAL DESCRIPTION

TMP432l AP is one version of single-chip microputer TLCS43 series processed with NMOS.

Since TMP4321AP can make periodic interrupt gained by dividing the CPU clock to 512 or 1024 using the built-in prescaler, it is most appropriate for puter control, such as sequence control.

Refer to the technical data of TLCS43 when using or considering TMP432l AP.

Features o Software patible with TLCS43 series o ROM capacity: 2048W x 8 Bits o RAM capacity: l28W x 4 Bits

0 Instruction executing rate: 4 ll S

0 Input ports: 3 x 4 Bits 0 Input/output ports: 2 x 4 Bits

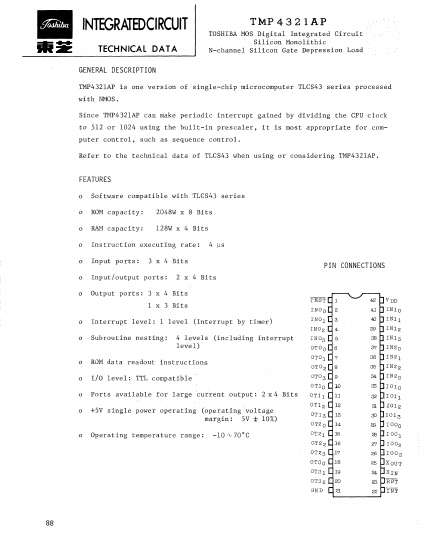

PIN CONNECTIONS

0 Output ports: 3 x 4 Bits x 3 Bits o Interrupt level: 1 level (Interrupt by timer) o Subroutine nesting: 4 levels (including interrupt level) a ROM data readout instructions o I/O level:- TTL patible o Ports available for large current output: 2 x 4 Bits o +5V single power operating (operating voltage m~rgin: 5V ± 10%) o Operating temperature range: -10" 70'C

TEST INDO INO] 1N02 IN03

OTOo OT01

OTD 2 OT03 OTIO

OT]] OTl2 OT13 DT20 OT21 OT 2 2 OT23 OT30 OT31 OT32 GND

VDD INIO INll IN12 1N13 IN20 IN21 IN22 1N23

101 0 1011 I 012 I013 100 0 1001 10°2 I00 3 XOUT XIN RST INT

INTEGRATEDCl RCUIT

TECHNICAL DATA

TIMER INTERRUPT

The following figure shows the configuration of timer interrupt c:ircuit of TMP4321AP.

X,N: 950 CLOCK ascf t::::I

Pll Ul E GENID-

LA---JRATOR

XOl1 ITV~DD:

-I INT

INTERNAL TIMING CLOCK ill Y IDER

TIME-BASH; COUNTER (;:J Bli Br NARY COUNTER)

Rg...