TMP8156P

DESCRIPTION

The TMP 8155P/8156P are RAM including I/O ports and counter/timer on the chip for using in the TLCS-85A microputer system. The RAM portion is designed with 2K bit static cells organized as 256 x 8. The 14 bit programmable counter/ timer is the down counter. It provides either a square wave or terminal count pulse for the cpu system depending on timer mode.

The I/O portion is consists of 2 programmable 8 bit I/O ports and 1 program~ mable 6 bit I/O port. The programmable I/O ports can be operated by BASIC MODE and STROBE MODE.

FEATURES patible with Intel's 8155/8516 Single '+5 V Power Supply Access Time: 400 ns (MAX.) Internal Address Latch 2 Programmable 8 Bit I/O Ports and 1 Programmable 6 Bit I/O Port. 256 Word x 8 Bits RAM Programmable 14 Bit Binary Counter/Timer Multiplexed Address and Data Bus Chip Enable Active High (TMP8l56P) or Low (TI!PS155P) 40 pin DIP

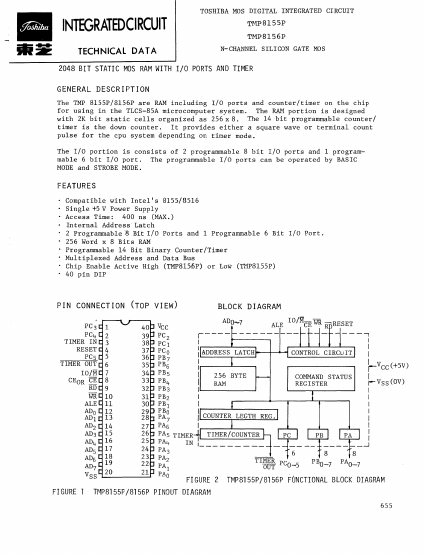

PIN CONNECTION (TOP VIEW)

BLOCK DIAGRAM

PC3

PC4 TIMER IN

RESET PCS

TIMER OUT

10/M CEOR CE

ALE ADO AD)...