Datasheet Summary

the use of system clock. I/O transactions are possible on every clock cycle. Range of operation frequencies, programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

Features

- -

- -

- - Performance Range: PC133. Burst Mode Operation. Auto and Self Refresh. LVTTL patible inputs and outputs. Single 3.3V + 0.3V power supply. MRS cycle with address key programs. Latency (Access from column address) Burst Length (1,2,4,8 & Full Page) Data Scramble (Sequential & Interleave)

- All inputs are sampled at the positive going edge of the system clock. w w

.D w t a

S a e h t e

U 4

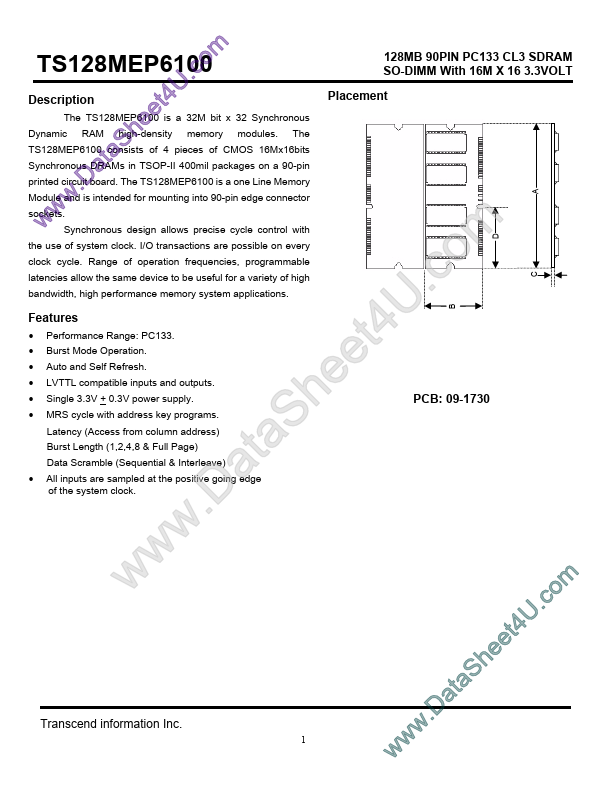

PCB: 09-1730

.c

D m o...