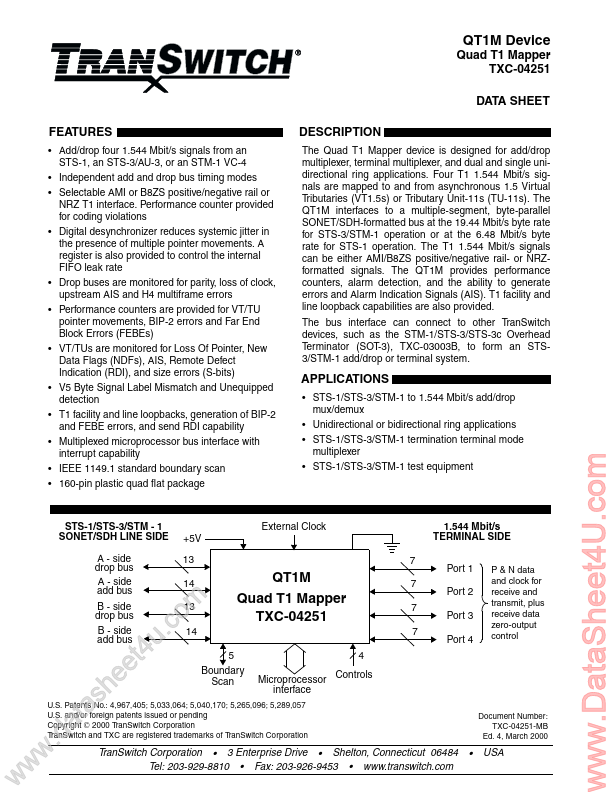

TXC-04251

FEATURES

- Add/drop four 1.544 Mbit/s signals from an STS-1, an STS-3/AU-3, or an STM-1 VC-4

- Independent add and drop bus timing modes

- Selectable AMI or B8ZS positive/negative rail or NRZ T1 interface. Performance counter provided for coding violations

- Digital desynchronizer reduces systemic jitter in the presence of multiple pointer movements. A register is also provided to control the internal FIFO leak rate

- Drop buses are monitored for parity, loss of clock, upstream AIS and H4 multiframe errors

- Performance counters are provided for VT/TU pointer movements, BIP-2 errors and Far End Block Errors (FEBEs)

- VT/TUs are monitored for Loss Of Pointer, New Data Flags (NDFs), AIS, Remote Defect Indication (RDI), and size errors (S-bits)

- V5 Byte Signal Label Mismatch and Unequipped detection

- T1 facility and line loopbacks, generation of BIP-2 and FEBE errors, and send RDI capability

- Multiplexed microprocessor bus interface with interrupt capability

- IEEE 1149.1 standard...