SI7114DN

SI7114DN is N-Channel 30-V Fast Switching MOSFET manufactured by Vaishali Semiconductor.

..

SPICE Device Model Si7114DN Vishay Siliconix N-Channel 30-V (D-S) Fast Switching MOSFET

CHARACTERISTICS

- N-Channel Vertical DMOS

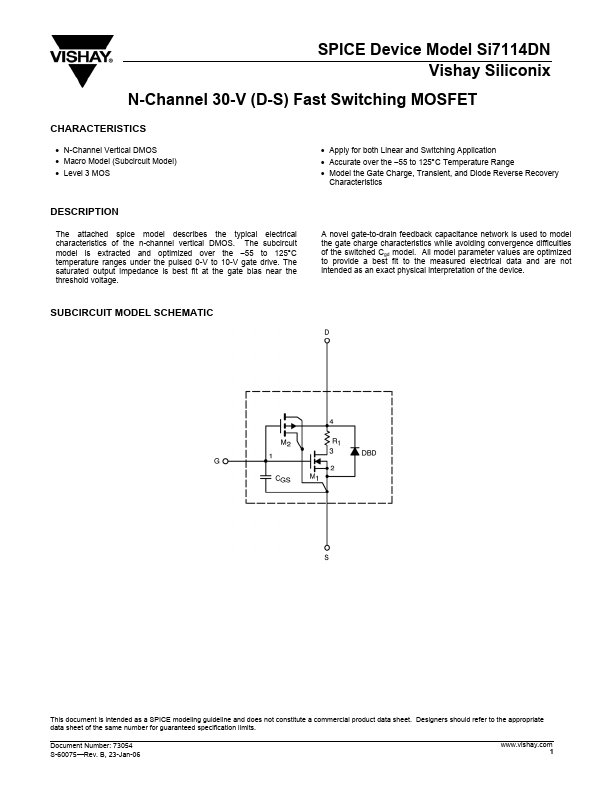

- Macro Model (Subcircuit Model)

- Level 3 MOS

- Apply for both Linear and Switching Application

- Accurate over the

- 55 to 125°C Temperature Range

- Model the Gate Charge, Transient, and Diode Reverse Recovery Characteristics

DESCRIPTION

The attached spice model describes the typical electrical characteristics of the n-channel vertical DMOS. The subcircuit model is extracted and optimized over the

- 55 to 125°C temperature ranges under the pulsed 0-V to 10-V gate drive. The saturated output impedance is best fit at the gate bias near the...