VT73LVP10MX

VT73LVP10MX is TTL to Differential LVPECL Translator manufactured by Vaishali Semiconductor.

Preliminary

VT73LVP10 TTL to Differential LVPECL Translator with Enable

Applications

- = PECL clock source

General Description

The Vaishali VT73LVP10 is a general purpose TTL (CMOS) to differential LVPECL translator, with active-LOW enable. The device operates from a single 3.3V supply. When /EN is LOW or open circuit, the device accepts an LVTTL or LVCMOS input and provides differential LVPECL outputs referenced to the positive supply rail. When /EN is HIGH, the Q output is set to the LOW state and QN output is set to the HIGH state.

Features

- =

- =

- =

- = 700ps typical propagation delay Differential LVPECL outputs Flow-through pinout -40 C to +85 C operating temperature range o o

- =

- =

- =

5V

- tolerant inputs ESD rating >2000V (Human Body Model) or >200V (Machine Model) Available as die, 8-pin SOIC or 8 pin MSOP package

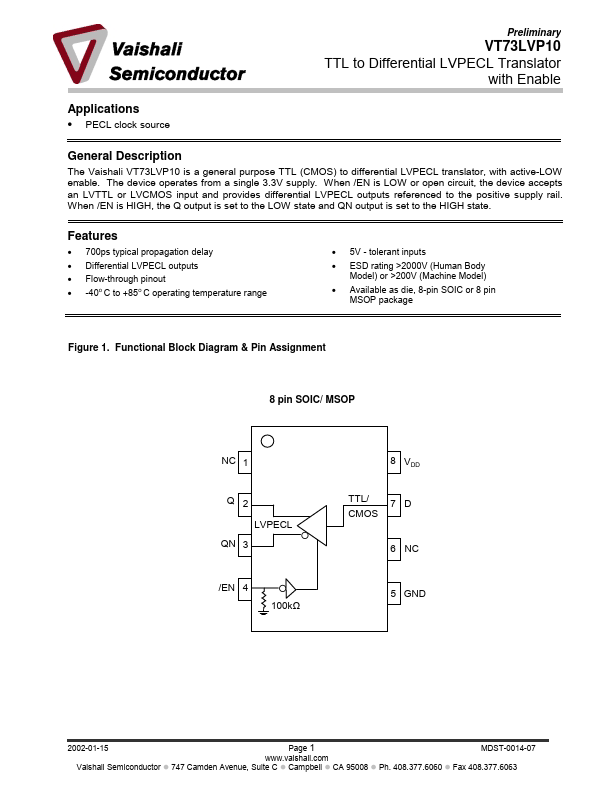

Figure 1. Functional Block Diagram & Pin Assignment

8 pin SOIC/ MSOP

NC 1

8 VDD

Q 2 LVPECL QN 3

TTL/ CMOS

7 D

6 NC

/EN 4 100kΩ

5 GND

2002-01-15 Vaishali Semiconductor

Page 1 .vaishali. 747 Camden Avenue, Suite C Campbell CA 95008

MDST-0014-07 Ph. 408.377.6060 Fax 408.377.6063

VT73LVP10...