GS810C

Description

- The GS809C and 810C are system supervisor circuits designed to monitor VCC in digital systems and provide a reset signal to the host processor when necessary. No external ponents are required.

- When the processor power supply voltage drops below the reset threshold, the reset output is driven active, in less than 40µs (TD1). Reset is maintained active for a time period (TD2), after the Vcc rises above the threshold voltage.

- To prevent jitter, the reset threshold voltage has a built-in hysteresis of 0.4% of VTH.

- The GS809C has an active-low reset output, while the GS810C has an active-high reset output. Both devices have push/pull output drives.

- The reset signal is guaranteed valid, down to Vcc = 1.0V.

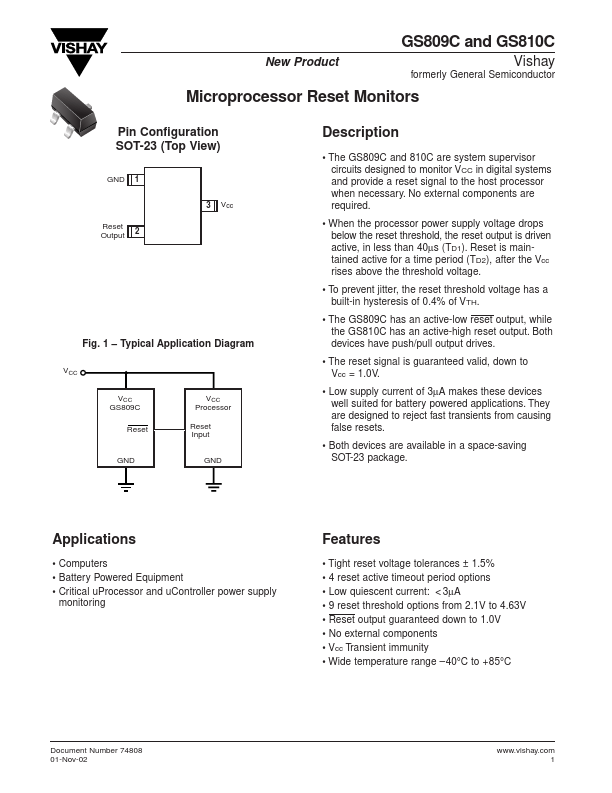

Fig. 1

- Typical Application Diagram

VCC VCC GS809C Reset VCC Processor Reset Input GND

- Low supply current of 3µA makes these devices well suited for battery powered applications. They are designed to reject fast transients from causing false resets.

- Both...