VSC6048

Features

- 8 Fully Integrated Timing Generators for ATE Applications

- 10/5ns Delay Range, 10ps Resolution

- Fully Digital Interface. No Off-Chip DACs or

Trim ponents Required

- ± 4 LSB Differential Non-Linearity

High-Speed Octal Programmable Timing Generator

- 100MHz/200MHz Dynamic Reprogram Frequency for Incrementing and Decrementing

- Internal or External High-Speed Clock Option

- Low Power: 8 Watts, max

- Low Cost 160-Pin PQFP Packaging

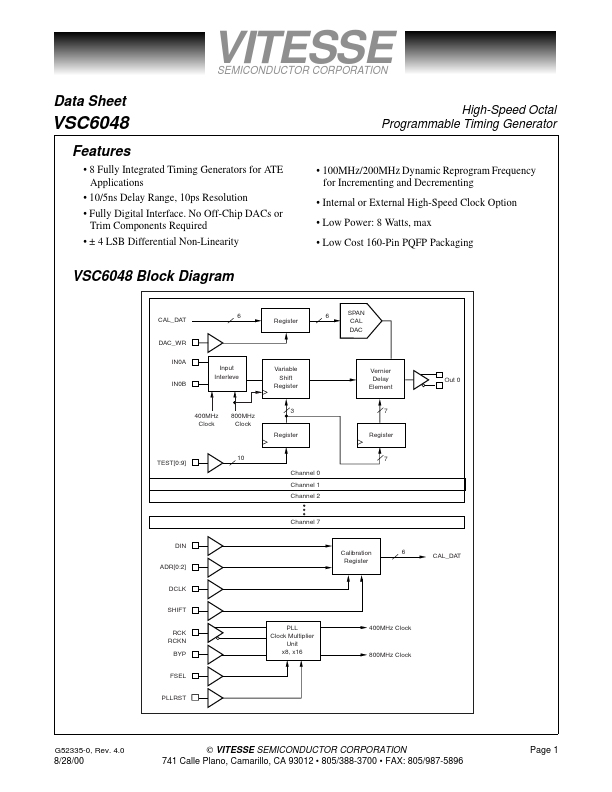

VSC6048 Block Diagram

CAL_DAT DAC_WR

IN0A IN0B

Input Interleve

Register

SPAN

Variable Shift

Register

Vernier Delay Element

400MHz 800MHz

Clock

Clock

3 Register

TEST[0:9]

Channel 0 Channel 1 Channel 2

7 Register

Out 0

DIN ADR[0:2]

DCLK SHIFT

RCK RCKN

BYP FSEL PLLRST

Channel 7

Calibration...