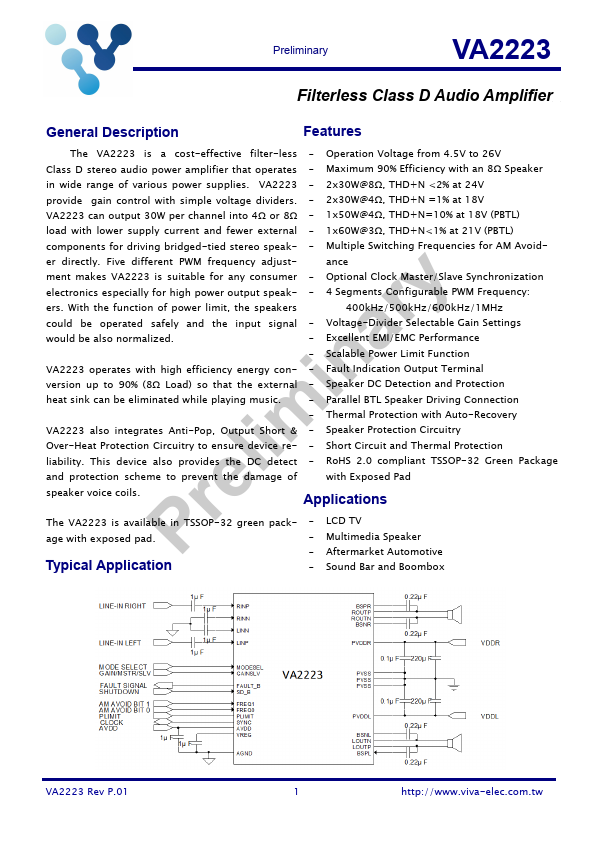

VA2223

Description

Features

Preliminary

The VA2223 is a cost-effective filter-less

- Operation Voltage from 4.5V to 26V

Class D stereo audio power amplifier that operates

- Maximum 90% Efficiency with an 8Ω Speaker in wide range of various power supplies. VA2223

- 2x30W@8Ω, THD+N <2% at 24V provide gain control with simple voltage dividers.

- 2x30W@4Ω, THD+N =1% at 18V

VA2223 can output 30W per channel into 4Ω or 8Ω

- 1x50W@4Ω, THD+N=10% at 18V (PBTL) load with lower supply current and fewer external

- 1x60W@3Ω, THD+N<1% at 21V (PBTL) ponents for driving bridged-tied stereo speak-

- Multiple Switching Frequencies for AM Avoid- er directly. Five different PWM frequency adjust- ance ment makes VA2223 is suitable for any consumer

- Optional Clock Master/Slave Synchronization electronics especially for high power output speak-

- 4 Segments Configurable PWM Frequency: ers. With the function of power limit, the speakers

400k Hz/500k Hz/600k Hz/1MHz could be operated safely and the...