Datasheet Summary

White Electronic Designs

68040 Features

Selection of Processor Speeds: 25, 33MHz Military Temperature Range: -55°C to +125°C Packaging

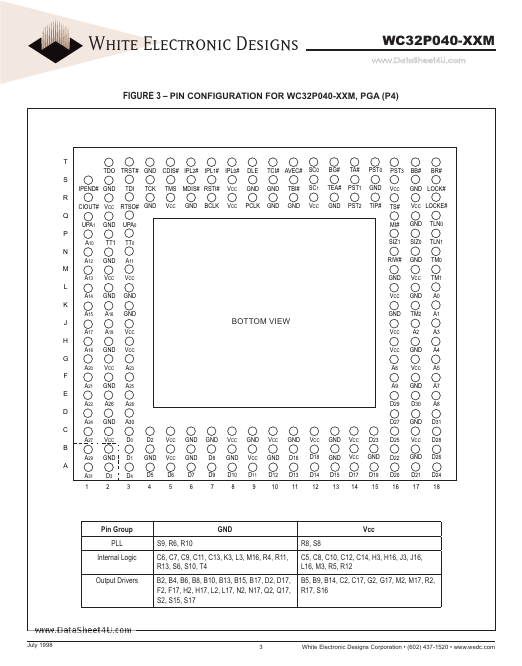

- 179 pin Ceramic PGA (P4)

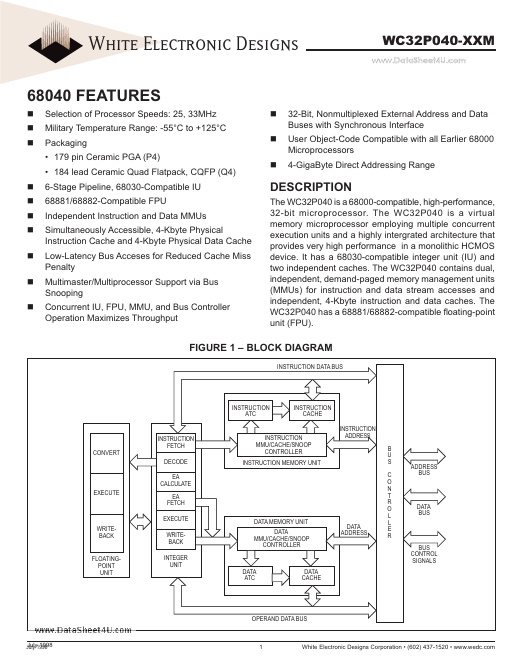

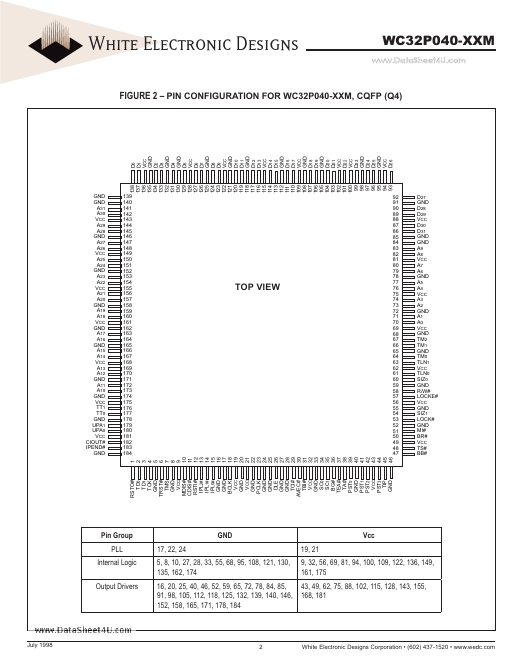

- 184 lead Ceramic Quad Flatpack, CQFP (Q4) 6-Stage Pipeline, 68030-patible IU 68881/68882-patible FPU Independent Instruction and Data MMUs Simultaneously Accessible, 4-Kbyte Physical Instruction Cache and 4-Kbyte Physical Data Cache Low-Latency Bus Acceses for Reduced Cache Miss Penalty Multimaster/Multiprocessor Support via Bus Snooping Concurrent IU, FPU, MMU, and Bus Controller Operation Maximizes Throughput

..

32-Bit, Nonmultiplexed External Address and Data Buses with Synchronous...