| Part | W3H32M72E-XSBX |

|---|---|

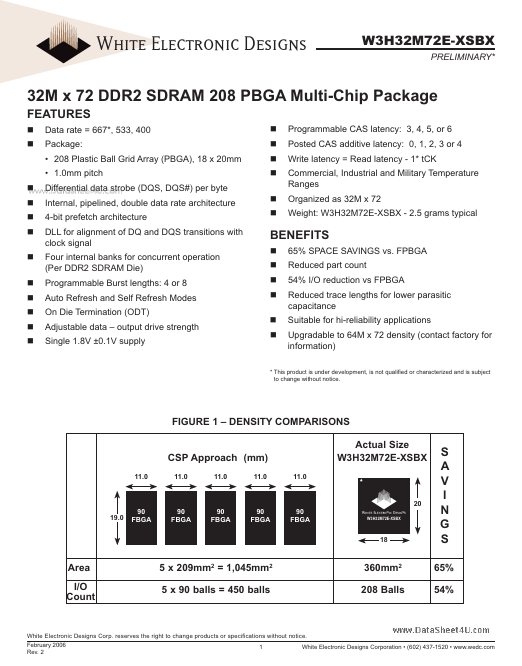

| Description | 32M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| Manufacturer | White Electronic Designs |

| Size | 965.20 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SOT23-6 | Zetex Semiconductors | Package information |

| SOT23-6 | Holtek Semiconductor | 6-pin Package Information |

| H-03-1 | Analog Devices | 3-Pin Metal Header Package |