WF512K32-xxx5

Key Features

- 66 pin, PGA Type, 1.075" square, Hermetic Ceramic HIP (Package 400 (1))

- 68 lead, 40mm, Low Capacitance Hermetic CQFP (Package 501)

- 68 lead, 40mm, Low Profile 3.5mm (0.140"), CQFP (Package 502)

- 68 lead, 22.4mm (0.880") Low Profile CQFP (G2U), 3.5mm (0.140") high, (Package 510)

- 68 lead, 23.9mm (0.940") Low Profile CQFP (G1U), 3.5mm (0.140") high, (Package 519) s 100,000 Erase/Program Cycles Minimum s Sector Architecture

- 8 equal size sectors of 64KBytes each

- Any combination of sectors can be concurrently erased. Also supports full chip erase s Organized as 512Kx32 s Commercial, Industrial and Military Temperature Ranges s 5 Volt Programming. 5V ± 10% Supply. s Low Power CMOS, 6.5mA Standby s Embedded Erase and Program Algorithms s TTL Compatible Inputs and CMOS Outputs s Built-in Decoupling Caps for Low Noise Operation s Page Program Operation and Internal Program Control Time s Weight WF512K32-XG2UX5 - 8 grams typical WF512K32-XH1X5 - 13 grams typical WF512K32-XG4X5 - 20 grams typical WF512K32-XG4TX5 - 20 grams typical WF512K32-XG1UX5 - 5 grams typical

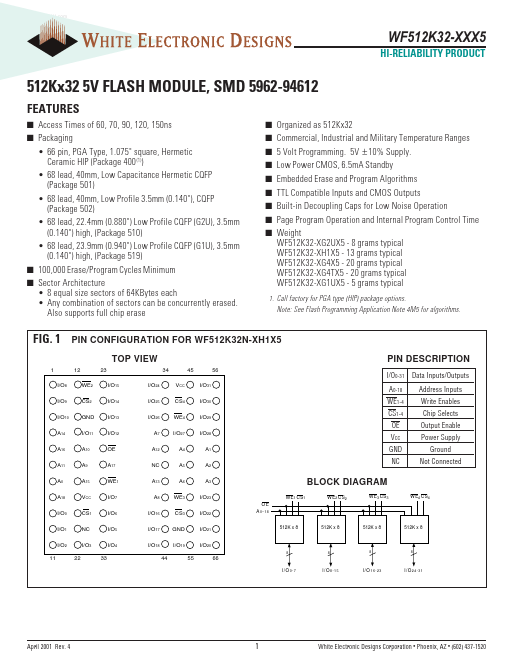

- Call factory for PGA type (HIP) package options. Note: See Flash Programming Application Note 4M5 for algorithms. FIG. 1