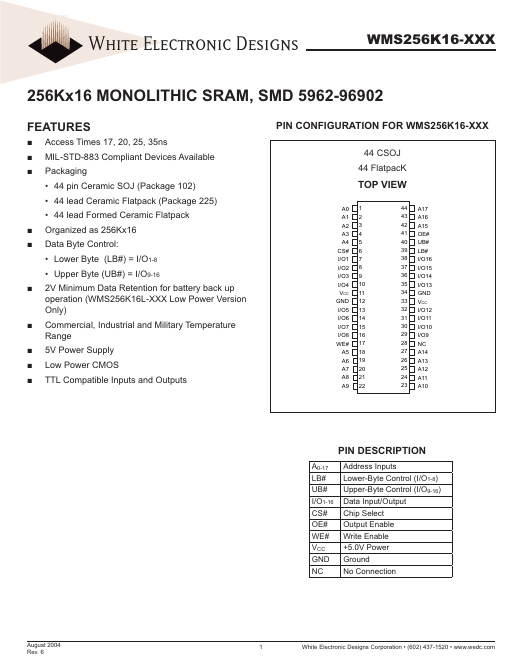

WMS256K16-xxx

Key Features

- Access Times 17, 20, 25, 35ns MIL-STD-883 compliant Devices Available Packaging

- 44 pin Ceramic SOJ (Package

- 44 lead Ceramic Flatpack (Package

- 44 lead Formed Ceramic Flatpack

- Organized as 256Kx16 Data Byte Control

- Lower Byte (LB#) = I/O1-8

- Upper Byte (UB#) = I/O9-16