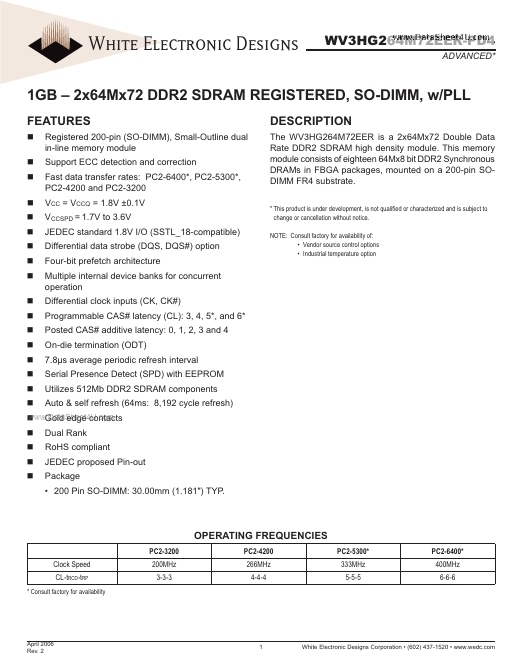

| Part | WV3HG264M72EER-PD4 |

|---|---|

| Description | 1GB - 2x64Mx72 DDR2 SDRAM REGISTERED |

| Manufacturer | White Electronic Designs |

| Size | 252.14 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74ALVCH162270 | Hitachi Semiconductor | 12-bit to 24-bit Registered Bus Exchanger with 3-state Outputs |

| HD74ALVCH162543 | Hitachi Semiconductor | 16-bit Registered Transceivers with 3-state Outputs |

| HD74ALVCHR162269A | Hitachi Semiconductor | 12-bit to 24-bit Registered Bus Exchanger with 3-state Outputs |