WF1M32B-XXX3

Key Features

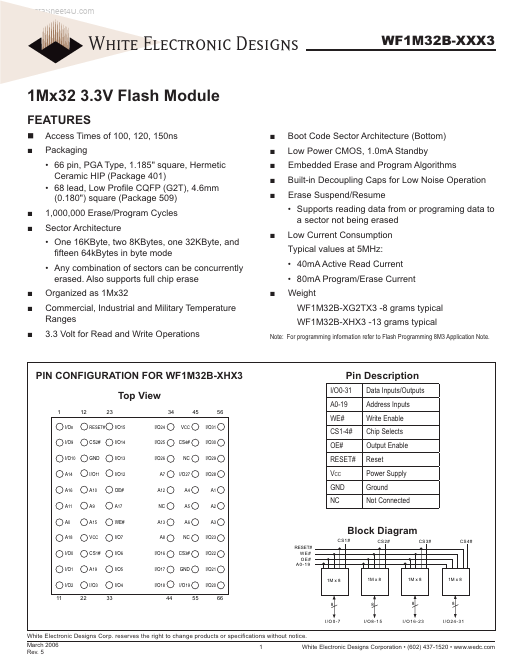

- Packaging

- 66 pin, PGA Type, 1.185" square, Hermetic Ceramic HIP (Package 401)

- 68 lead, Low Profile CQFP (G2T), 4.6mm (0.180") square (Package 509) *

- 1,000,000 Erase/Program Cycles Sector Architecture

- One 16KByte, two 8KBytes, one 32KByte, and fifteen 64kBytes in byte mode

- Any combination of sectors can be concurrently erased. Also supports full chip erase * *

- Organized as 1Mx32 Commercial, Industrial and Military Temperature Ranges 3.3 Volt for Read and Write Operations * * * * * *

- WF1M32B-XXX3 Boot Code Sector Architecture (Bottom) Low Power CMOS, 1.0mA Standby Embedded Erase and Program Algorithms Built-in Decoupling Caps for Low Noise Operation Erase Suspend/Resume

- Supports reading data from or programing data to a sector not being erased Low Current Consumption Typical values at 5MHz:

- 40mA Active Read Current