W25P022A

Description

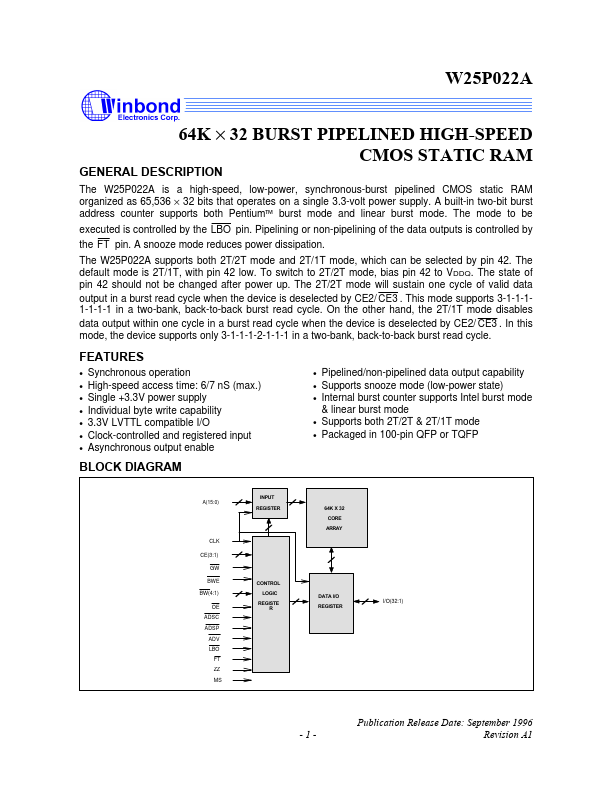

The W25P022A is a high-speed, low-power, synchronous-burst pipelined CMOS static RAM organized as 65,536 × 32 bits that operates on a single 3.3-volt power supply.

Key Features

- Synchronous operation

- High-speed access time: 6/7 nS (max.)

- Single +3.3V power supply

- Individual byte write capability

- Clock-controlled and registered input

- Asynchronous output enable