W25P243A

Description

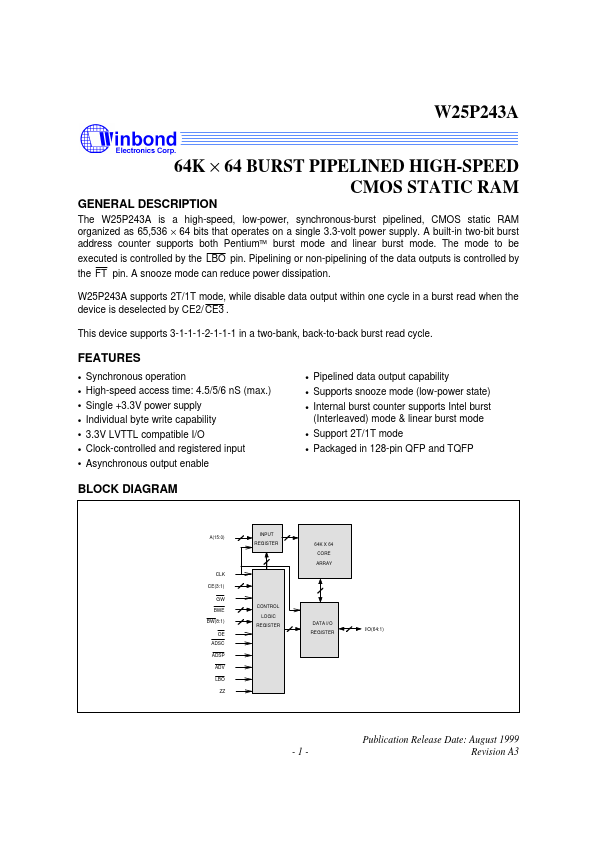

The W25P243A is a high-speed, low-power, synchronous-burst pipelined, CMOS static RAM organized as 65,536 × 64 bits that operates on a single 3.3-volt power supply.

Key Features

- Synchronous operation

- Single +3.3V power supply

- Individual byte write capability

- Clock-controlled and registered input

- Asynchronous output enable

- Pipelined data output capability

- Supports snooze mode (low-power state)

- Internal burst counter supports Intel burst (Interleaved) mode & linear burst mode

- Support 2T/1T mode

- Packaged in 128-pin QFP and TQFP