W83178S

W83178S is 100 MHZ 3-DIMM SDRAM BUFFER manufactured by Winbond.

100MHZ 3-DIMM SDRAM BUFFER

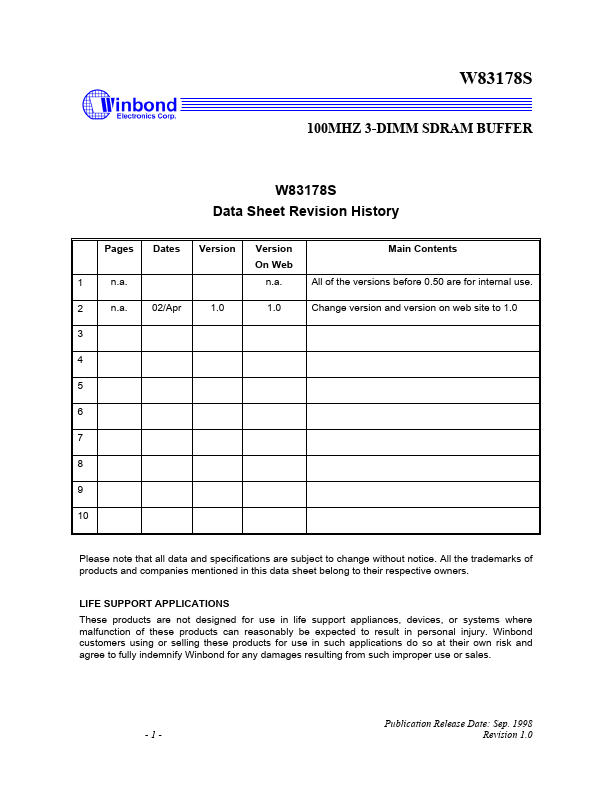

W83178S Data Sheet Revision History

Pages 1 2 3 4 5 6 7 8 9 10 n.a. n.a. 02/Apr 1.0 Dates Version Version On Web n.a. 1.0 All of the versions before 0.50 are for internal use. Change version and version on web site to 1.0 Main Contents

Please note that all data and specifications are subject to change without notice. All the trademarks of products and panies mentioned in this data sheet belong to their respective owners. LIFE SUPPORT APPLICATIONS These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or...