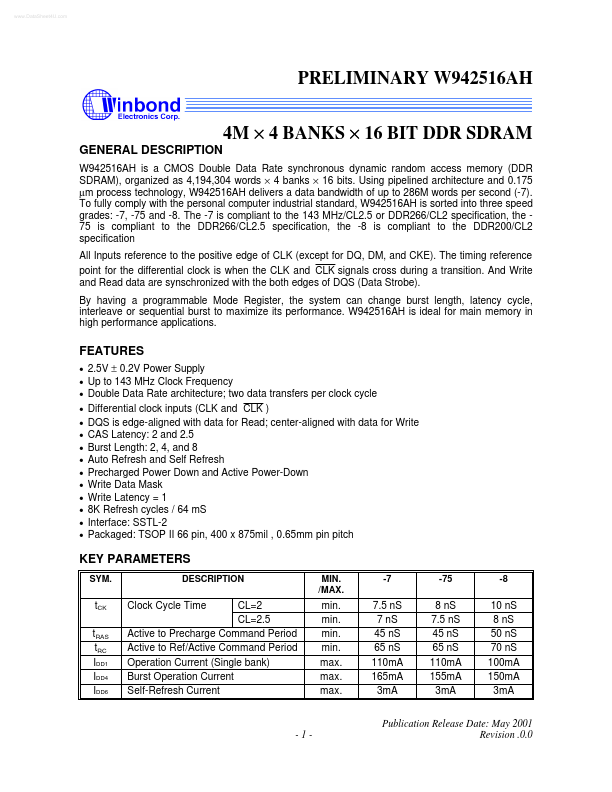

W942516AH

Description

W942516AH is a CMOS Double Data Rate synchronous dynamic random access memory (DDR SDRAM), organized as 4,194,304 words × 4 banks × 16 bits.

Key Features

- 2.5V ± 0.2V Power Supply

- Up to 143 MHz Clock Frequency

- Double Data Rate architecture; two data transfers per clock cycle

- Differential clock inputs (CLK and CLK )

- DQS is edge-aligned with data for Read; center-aligned with data for Write

- CAS Latency: 2 and 2.5

- Auto Refresh and Self Refresh

- Precharged Power Down and Active Power-Down

- Write Data Mask

- Write Latency = 1