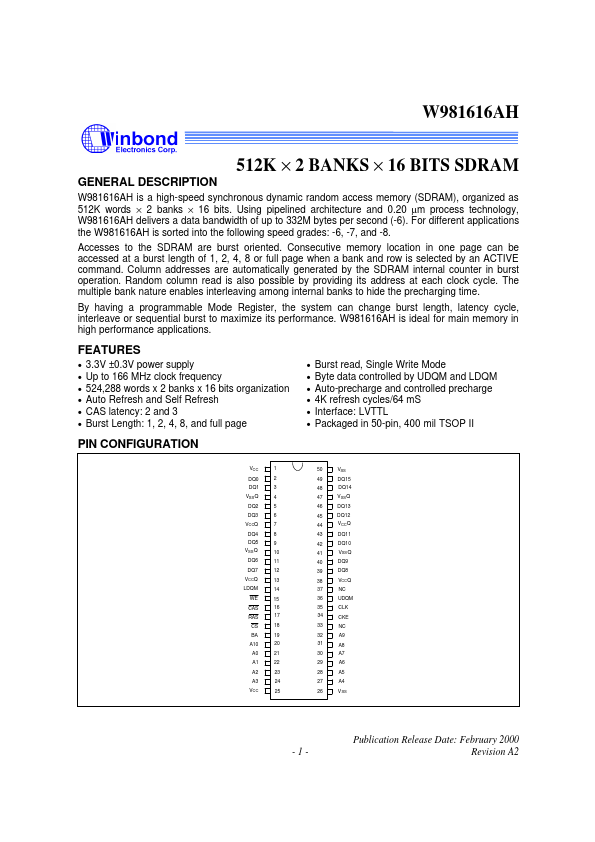

W981616AH

W981616AH is 512K x 2 BANKS x 16-BIT SDRAM manufactured by Winbond.

512K × 2 BANKS × 16 BITS SDRAM

GENERAL DESCRIPTION

W981616AH is a high-speed synchronous dynamic random access memory (SDRAM), organized as 512K words × 2 banks × 16 bits. Using pipelined architecture and 0.20 µm process technology, W981616AH delivers a data bandwidth of up to 332M bytes per second (-6). For different applications the W981616AH is sorted into the following speed grades: -6, -7, and -8.

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE mand. Column addresses are automatically generated by the SDRAM internal counter in burst...