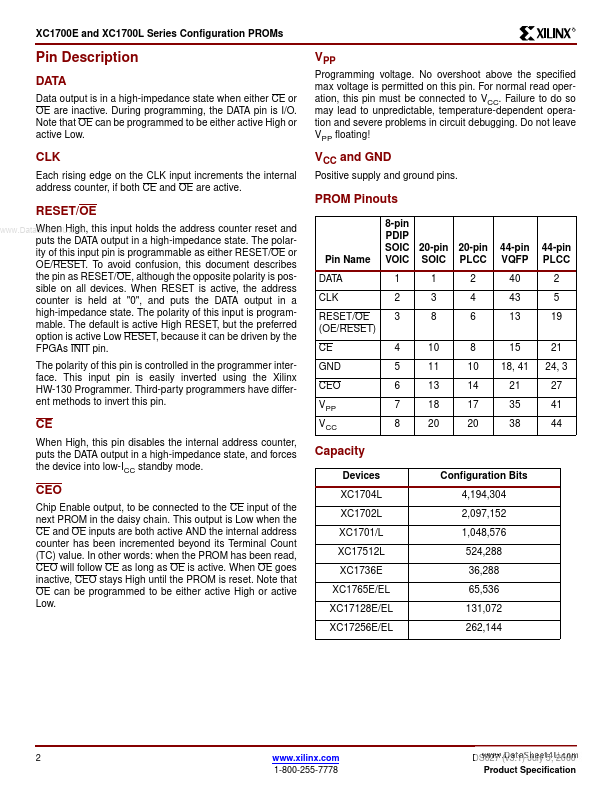

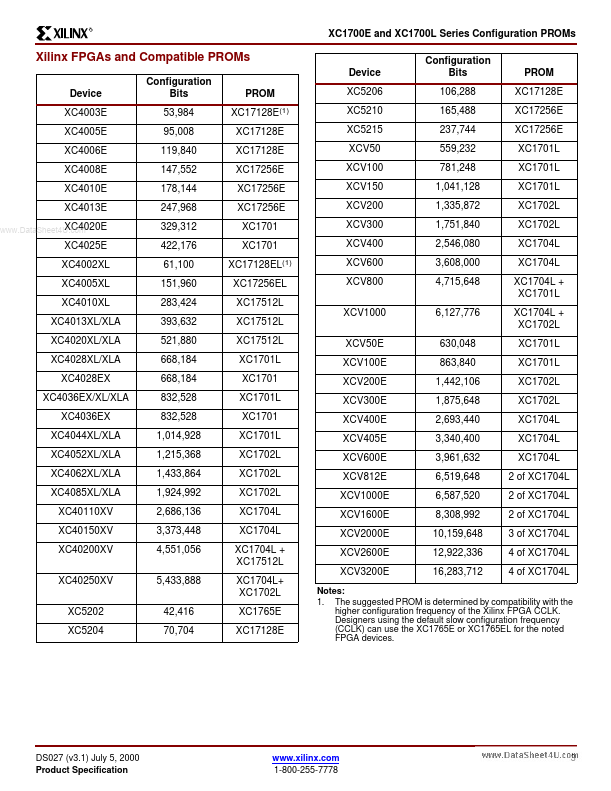

Datasheet Summary

XC1700E and XC1700L Series Configuration PROMs

0 8

DS027 (v3.1) July 5, 2000

Product Specification

Features

- One-time programmable (OTP) read-only memory designed to store configuration bitstreams of Xilinx FPGA devices Simple interface to the FPGA; requires only one user I/O pin Cascadable for storing longer or multiple bitstreams Programmable reset polarity (active High or active Low) for patibility with different FPGA solutions XC17128E/EL, XC17256E/EL, XC1701 and XC1700L series support fast configuration Low-power CMOS Floating Gate process XC1700E series are available in 5V and 3.3V versions XC1700L series are available in 3.3V only Available in pact plastic packages:...