17S15APC

17S15APC is Spartan-II/Spartan-IIE Family OTP Configuration PROMs manufactured by Xilinx.

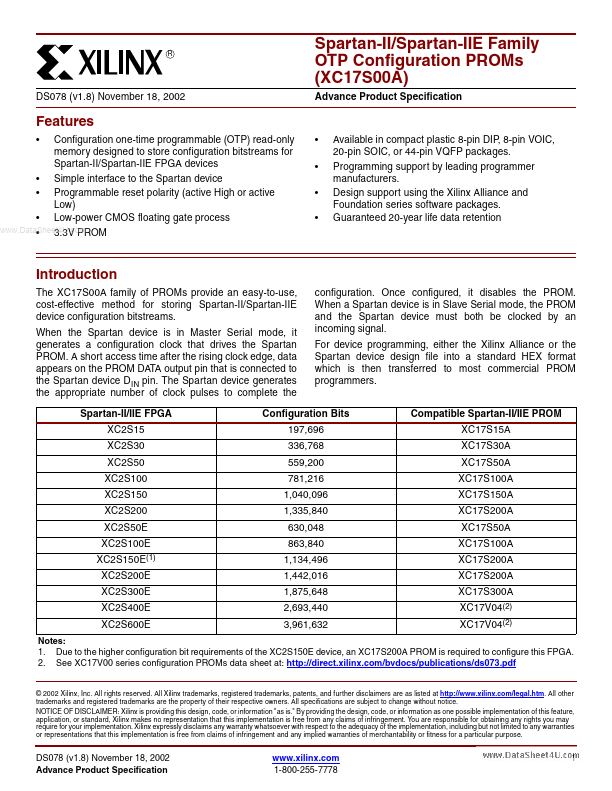

Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

DS078 (v1.8) November 18, 2002

Advance Product Specification

Features

Configuration one-time programmable (OTP) read-only memory designed to store configuration bitstreams for Spartan-II/Spartan-IIE FPGA devices

- Simple interface to the Spartan device

- Programmable reset polarity (active High or active Low)

- Low-power CMOS floating gate process ..

- 3.3V PROM

- -

- -

- Available in pact plastic 8-pin DIP, 8-pin VOIC, 20-pin SOIC, or 44-pin VQFP packages. Programming support by leading programmer manufacturers. Design support using the Xilinx Alliance and Foundation series software...