9536XL Overview

Key Specifications

Package: TQFP

Mount Type: Surface Mount

Pins: 44

Operating Voltage: 3.3 V

Key Features

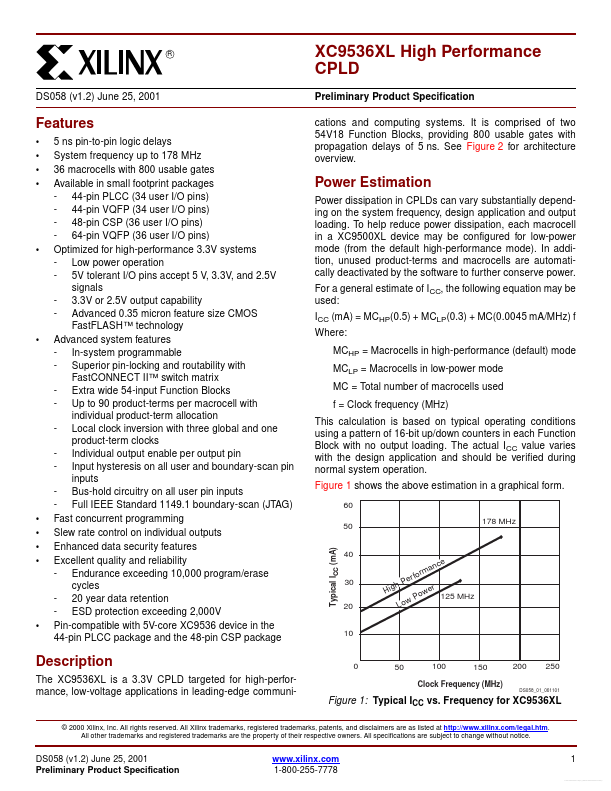

- 5 ns pin-to-pin logic delays System frequency up to 178 MHz 36 macrocells with 800 usable gates Available in small footprint packages

- 44-pin PLCC (34 user I/O pins)

- 44-pin VQFP (34 user I/O pins)

- 48-pin CSP (36 user I/O pins)

- 64-pin VQFP (36 user I/O pins) Optimized for high-performance 3.3V systems

- Low power operation

- 5V tolerant I/O pins accept 5 V, 3.3V, and 2.5V signals

- 3.3V or 2.5V output capability

- Advanced 0.35 micron feature size CMOS FastFLASH™ technology Advanced system features

- In-system programmable