VIRTEX-4

Description

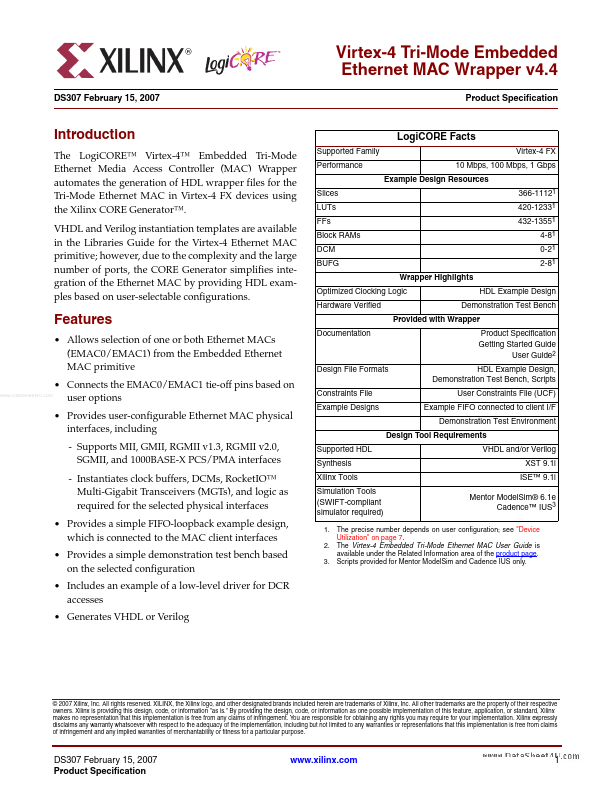

The LogiCORE™ Virtex-4™ Embedded Tri-Mode Ethernet Media Access Controller (MAC) Wrapper automates the generation of HDL wrapper files for the Tri-Mode Ethernet MAC in Virtex-4 FX devices using the Xilinx CORE Generator™. VHDL and Verilog instantiation templates are available in the Libraries Guide for the Virtex-4 Ethernet MAC primitive; however, due to the complexity and the large number of ports, the CORE Generator simplifies integration of the Ethernet MAC by providing HDL examples based on user-selectable configurations.

Key Features

- Allows selection of one or both Ethernet MACs (EMAC0/EMAC1) from the Embedded Ethernet MAC primitive Design File Formats Constraints File Example Designs

- Connects the EMAC0/EMAC1 tie-off pins based on user options

- Provides user-configurable Ethernet MAC physical interfaces, including - Supports MII, GMII, RGMII v1.3, RGMII v2.0, SGMII, and 1000BASE-X PCS/PMA interfaces - Instantiates clock buffers, DCMs, RocketIO™ Multi-Gigabit Transceivers (MGTs), and logic as required for the selected physical interfaces

- Provides a simple FIFO-loopback example design, which is connected to the MAC client interfaces

- Provides a simple demonstration test bench based on the selected configuration

- Includes an example of a low-level driver for DCR accesses

- Generates VHDL or Verilog

- The precise number depends on user configuration; see "Device Utilization" on page 7.

- The Virtex-4 Embedded Tri-Mode Ethernet MAC User Guide is available under the Related Information area of the product page.

- Scripts provided for Mentor ModelSim and Cadence IUS only. © 2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners. Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. DS307 February 15, 2007 Product Specification