XC2V1000-5FG456I

XC2V1000-5FG456I is Field-Programmable Gate Arrays manufactured by Xilinx.

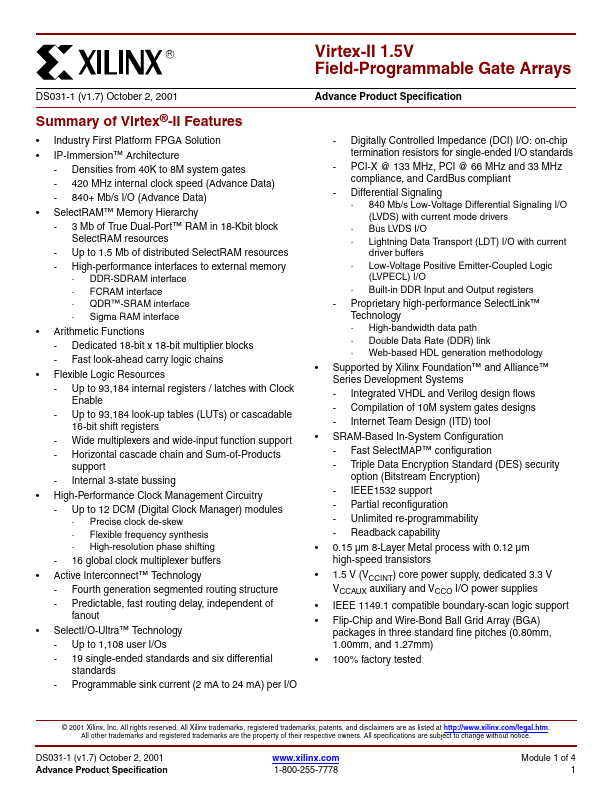

Features

- - Industry First Platform FPGA Solution IP-Immersion™ Architecture

- Densities from 40K to 8M system gates

- 420 MHz internal clock speed (Advance Data)

- 840+ Mb/s I/O (Advance Data) Select RAM™ Memory Hierarchy

- 3 Mb of True Dual-Port™ RAM in 18-Kbit block Select RAM resources

- Up to 1.5 Mb of distributed Select RAM resources

- High-performance interfaces to external memory

- DDR-SDRAM interface

- FCRAM interface

- QDR™-SRAM interface

- Sigma RAM interface Arithmetic Functions

- Dedicated 18-bit x 18-bit multiplier blocks

- Fast look-ahead carry logic chains Flexible Logic Resources

- Up to 93,184 internal registers / latches with Clock Enable

- Up to 93,184 look-up tables (LUTs) or cascadable 16-bit shift registers

- Wide multiplexers and wide-input function support

- Horizontal cascade chain and Sum-of-Products support

- Internal 3-state bussing High-Performance Clock Management Circuitry

- Up to 12 DCM (Digital Clock Manager) modules

- Precise clock de-skew

- Flexible frequency synthesis

- High-resolution phase shifting

- 16 global clock multiplexer buffers Active Interconnect™ Technology

- Fourth generation segmented routing structure

- Predictable, fast routing delay, independent of fanout Select I/O-Ultra™ Technology

- Up to 1,108 user I/Os

- 19 single-ended standards and six differential standards

- Programmable sink current (2 m A to 24 m A) per I/O Digitally Controlled Impedance (DCI) I/O: on-chip termination resistors for single-ended I/O standards

- PCI-X @ 133 MHz, PCI @ 66 MHz and 33 MHz pliance, and Card Bus pliant

- Differential Signaling

- 840 Mb/s Low-Voltage Differential Signaling I/O (LVDS) with current mode drivers

- Bus LVDS I/O

- Lightning Data Transport (LDT) I/O with current driver buffers

- Low-Voltage Positive Emitter-Coupled Logic (LVPECL) I/O

- Built-in DDR Input and Output registers

- Proprietary high-performance Select Link™ Technology

- High-bandwidth data path

- Double Data Rate (DDR) link

- Web-based HDL generation...