XCR3032XL-5PC44I

Description

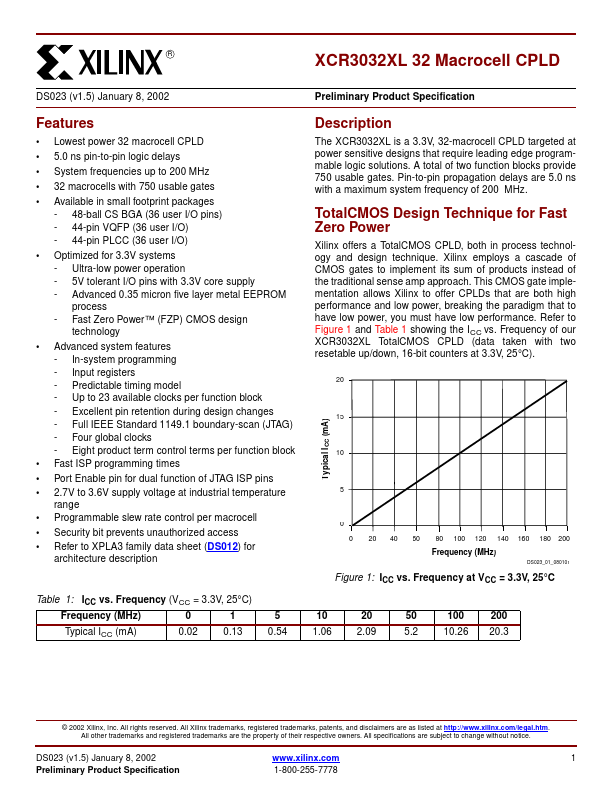

The XCR3032XL is a 3.3V, 32-macrocell CPLD targeted at power sensitive designs that require leading edge programmable logic solutions. A total of two function blocks provide 750 usable gates.

Key Features

- 48-ball CS BGA (36 user I/O pins)

- 44-pin VQFP (36 user I/O)

- 44-pin PLCC (36 user I/O) Optimized for 3.3V systems

- Ultra-low power operation

- 5V tolerant I/O pins with 3.3V core supply

- Advanced 0.35 micron five layer metal EEPROM process

- Fast Zero Power™ (FZP) CMOS design technology Advanced system features

- In-system programming

- Input registers

- Predictable timing model