XCV100E

XCV100E is 1.8V Field Programmable Gate Arrays manufactured by Xilinx.

- OBSOLETE

- OBSOLETE

- OBSOLETE

- OBSOLETE

- 0

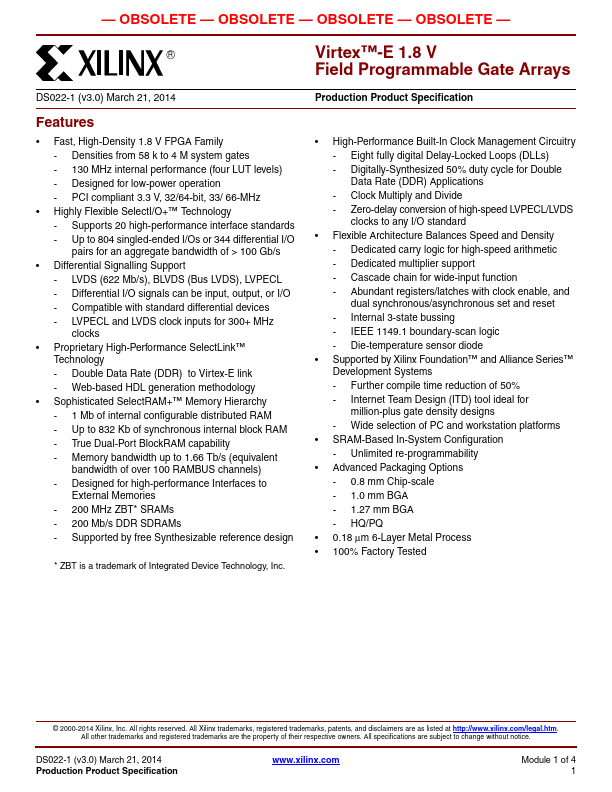

R Virtex™-E 1.8 V Field Programmable Gate Arrays

DS022-1 (v3.0) March 21, 2014

Features

- Fast, High-Density 1.8 V FPGA Family

- Densities from 58 k to 4 M system gates

- 130 MHz internal performance (four LUT levels)

- Designed for low-power operation

- PCI pliant 3.3 V, 32/64-bit, 33/ 66-MHz

- Highly Flexible SelectI/O+™ Technology

- Supports 20 high-performance interface standards

- Up to 804 singled-ended I/Os or 344 differential I/O pairs for an aggregate bandwidth of > 100 Gb/s

- Differential Signalling Support

- LVDS (622 Mb/s), BLVDS (Bus LVDS), LVPECL

- Differential I/O signals can be input, output, or I/O

- patible with...