YSS932 Datasheet Text

YSS932

AC3D3B

96kHz DIR + Dolby Digital / Pro Logic II / DTS decoder + Sub DSP

OUTLINE

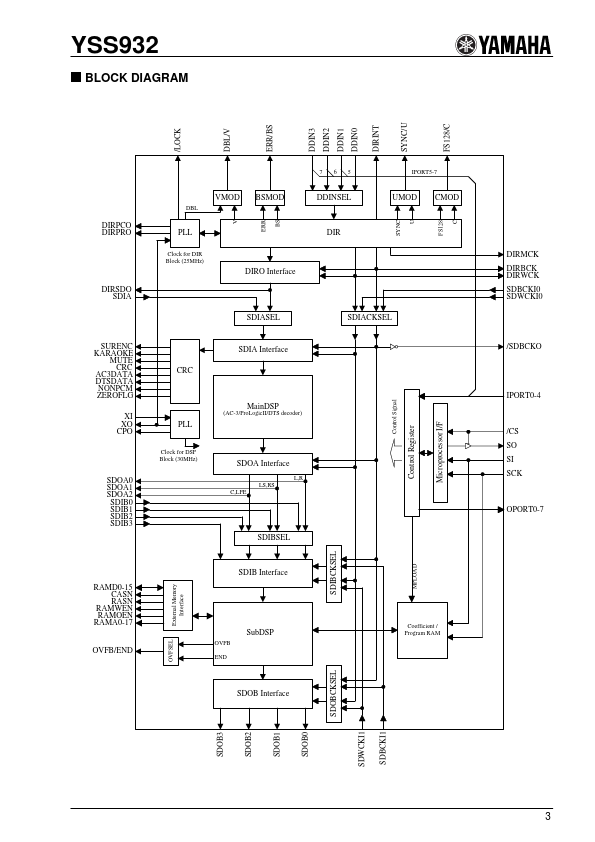

YSS932 is one chip LSI consisting of three built-in blocks : SPDIF receiver (DIR), Dolby Digital (AC-3) / Pro Logic II & DTS decoder (Main DSP) and programmable sound fields processing DSP (Sub DSP). The Sub DSP is capable of realizing various sound fields, such as virtual surround by down-loading the program and coefficient from outside.

Features

[ DIR Block ]

- Sampling frequency: Two ranges are available including; 32k to 48kHz (normal rate) and 64k to 96kHz (double rate).

- Provides master clock, 256fs, to DAC, ADC and the other peripheral devices. The clock output can be controlled with various modes determined by register settings.

- Has a pin that indicates the double rate operation.

- Every channel status and user data can be read through the microprocessor interface.

- Has an output pin for interrupt that is activated by changing of the status information.

- Internal operation frequency: 25MHz [ Main DSP Block ]

- Dolby Digital (AC-3) / Pro Logic II and DTS decode.

- High quality internal 24 bit DSP.

- No external memory is required. (Memory for the center and surround channel signal delay is included.)

- AC-3 Karaoke mode.

- Supports pression mode at AC-3 / DTS decoding.

- Included de-emphasis filter for the PCM signal.

- Pro Logic II decoding for Dolby Digital 2 channels decoded signal as well as ordinary PCM signal.

- Reads Dolby Digital / DTS decode information through the microprocessor interface.

- Internal operation frequency: 30MHz

YAMAHA CORPORATION

..

YSS932 CATALOG CATALOG No.: LSI-4SS932A2 2003.2

YSS932

[ Sub DSP Block ]

- Capable of realizing various sound fields, such as simulation surround, output configuration and virtual surround by...