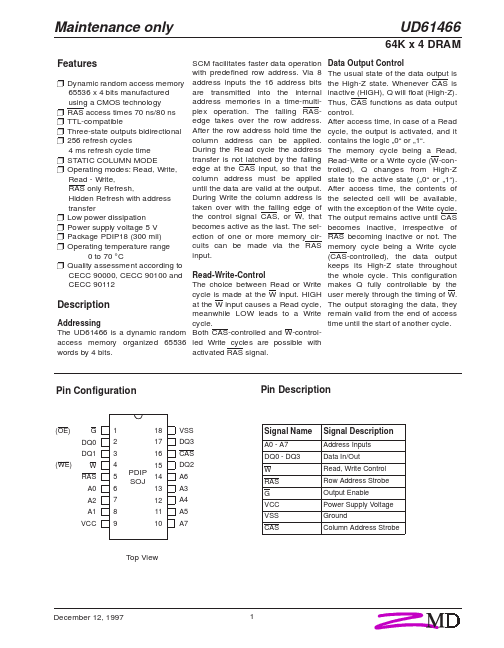

UD61466

Key Features

- UD61466 64K x 4 DRAM SCM facilitates faster data operation with predefined row address

- Via 8 address inputs the 16 address bits are transmitted into the internal address memories in a time-multiplex operation

- The falling RASedge takes over the row address

- After the row address hold time the column address can be applied

- During Write the column address is taken over with the falling edge of the control signal CAS, or W, that bees active as the last

- The selection of one or more memory circuits can be made via the RAS input

- Data Output Control The usual state of the data output is the High-Z state

- Whenever CAS is inactive (HIGH), Q will float (High-Z)

- Thus, CAS functions as data output control

- After access time, in case of a Read cycle, the output is activated, and it contains the logic „0“ or „1“