Datasheet Summary

GP4020

GPS Receiver Baseband Processor

DS5134

ISSUE 4.4

May 2002

Features

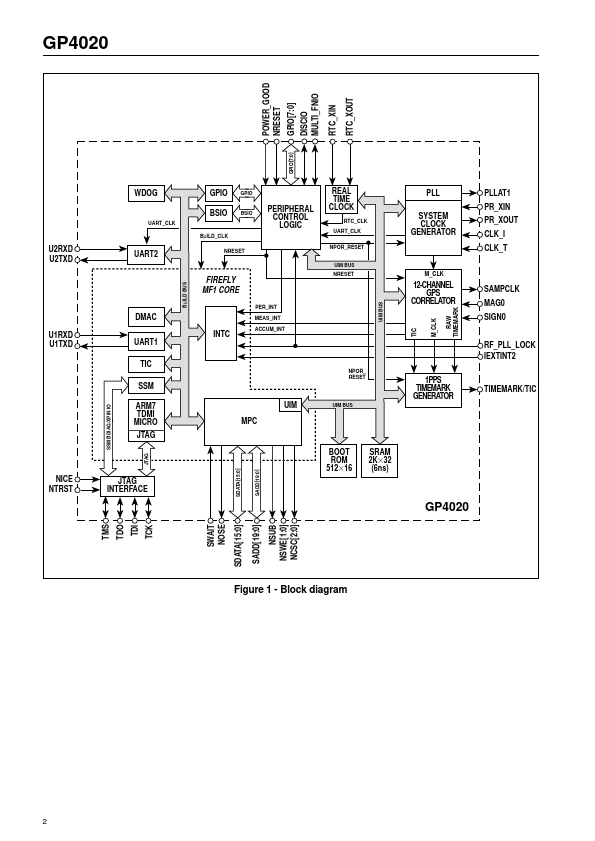

- plete GPS correlator and Firefly MF1 microcontroller core

- ARM 7TDMITM (Thumb®) Microprocessor, with JTAG ICEBreakerTM Debug Interface

- Fully Configurable External Data Bus

- 12 Fully Independent Correlation Channels

- Low Voltage Operation: 3- 3V

- Low Current Power- Down Mode

- 1PPS UTC Aligned Timing Output

- Dual UART

- 3-wire BµILD Serial Input/Output (BSIO) Interface

- 8 General Purpose Input/Output (GPIO) Lines

- Boot ROM, allowing Software Upload via UART

- 8K Bytes Internal SRAM

- patible with GP2015 and GP2010 RF Front Ends

Ordering Information

GP4020/IG/GQ1N (trays) GP4020/IG/GQ1Q (tape and...