CLA200

Overview

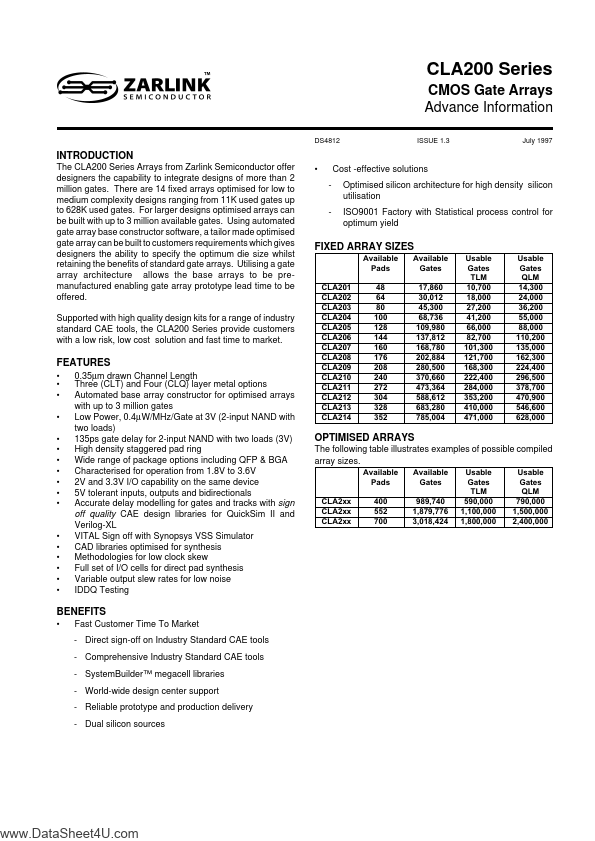

The CLA200 Series Arrays from Zarlink Semiconductor offer designers the capability to integrate designs of more than 2 million gates. There are 14 fixed arrays optimised for low to medium complexity designs ranging from 11K used gates up to 628K used gates.

- 0.35µm drawn Channel Length Three (CLT) and Four (CLQ) layer metal options Automated base array constructor for optimised arrays with up to 3 million gates Low Power, 0.4µ W/MHz/Gate a