MT9075B

MT9075B is E1 Single Chip Transceiver manufactured by Zarlink Semiconductor.

Features

- bined PCM 30 framer, Line Interface Unit (LIU) and link controllers in a 68 pin PLCC or 100 pin MQFP package Selectable bit rate data link access with optional Sa bits HDLC controller (HDLC0) and channel 16 HDLC controller (HDLC1) LIU dynamic range of 20 d B Enhanced performance monitoring and programmable error insertion functions Low jitter DPLL for clock generation Operating under synchronized or free run mode Two-frame receive elastic buffer with controlled slip direction indication Selectable transmit or receive jitter attenuator Intel or Motorola non-multiplexed parallel microprocessor interface CRC-4 updating algorithm for intermediate path points of a message-based data link application ST-BUS/GCI 2.048 Mbit/s backplane bus for both data and signalling Ordering Information MT9075BPR 68 Pin PLCC MT9075BL 100 Pin MQFP MT9075BP 68 Pin PLCC MT9075BPR1 68 Pin PLCC- MT9075BP1 68 Pin PLCC- MT9075BL1 100 Pin MQFP-

- Pb Free Matte Tin -40° C to +85 ° C Tape & Reel Trays Tubes Tape & Reel Tubes Trays

August 2005

- -

- -

- -

- -

- -

Applications

- -

- - E1 add/drop multiplexers and channel banks CO and PBX equipment interfaces Primary Rate ISDN nodes Digital Cross-connect Systems (DCS)

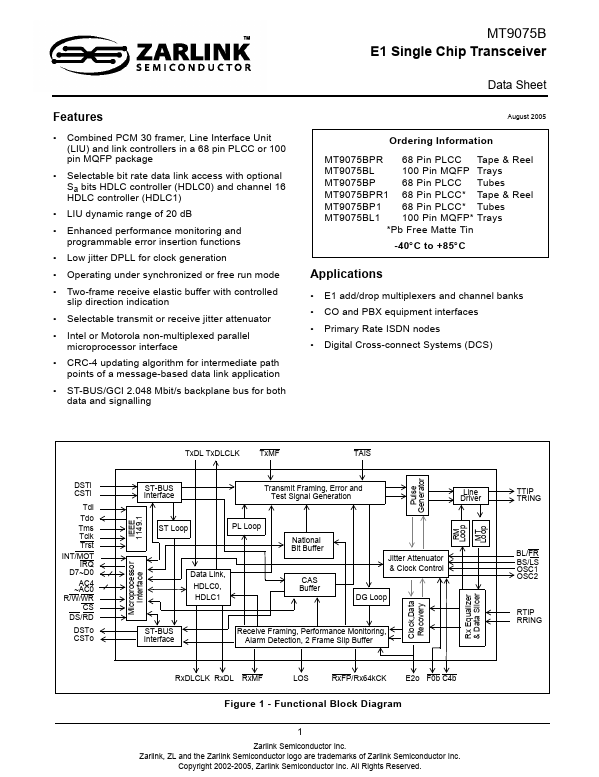

Tx DL Tx DLCLK

Tx MF

TAIS

DSTi CSTi Tdi Tdo Tms Tclk Trst INT/MOT IRQ D7~D0 AC4 ~AC0 R/W/WR CS DS/RD DSTo CSTo IEEE 1149.1

ST-BUS Interface

Transmit Framing, Error and Test Signal Generation

Pulse Generator

Line Driver

TTIP TRING

RM Loop

National Bit Buffer Data Link, HDLC0, HDLC1 Jitter Attenuator & Clock Control CAS Buffer

MT Loop

ST Loop

PL Loop

Microprocessor Interface

BL/FR BS/LS OSC1 OSC2 Rx Equalizer & Data Slicer

Clock,Data Recovery

DG Loop

RTIP RRING

ST-BUS Interface

Receive Framing, Performance Monitoring, Alarm Detection, 2 Frame Slip Buffer

Rx DLCLK Rx DL

Rx MF

Rx FP/Rx64k CK

E2o F0b C4b

Figure 1

- Functional Block Diagram...