SP5610 Overview

Key Specifications

Package: VQFN

Mount Type: Surface Mount

Pins: 56

Operating Voltage: 3.3 V

Key Features

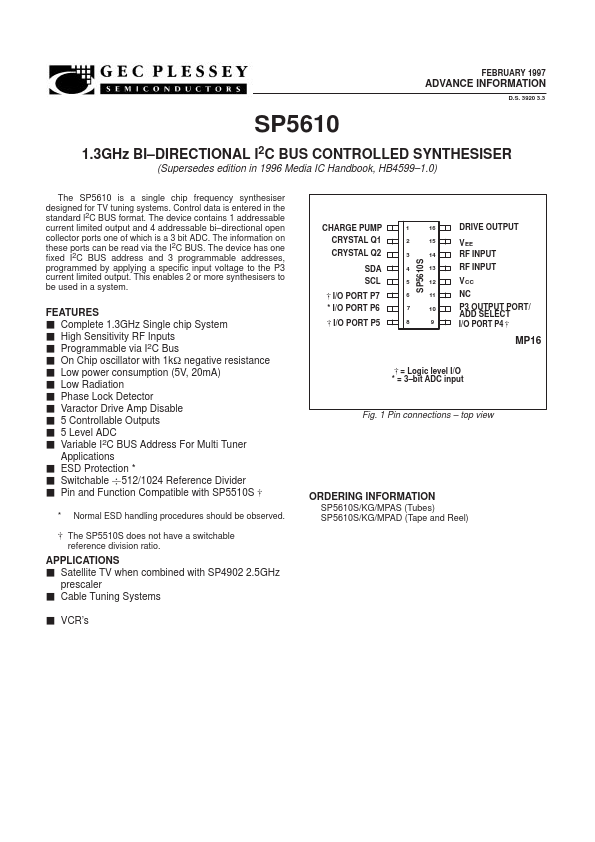

- DIRECTIONAL I2C BUS CONTROLLED SYNTHESISER

- directional open collector ports one of which is a 3 bit ADC. The information on these ports can be read via the I2C BUS. The device has one fixed I2C BUS address and 3 programmable addresses, programmed by applying a specific input voltage to the P3 current limited output. This enables 2 or more synthesisers to be used in a system