VP16256

VP16256 is Programmable FIR FIlter manufactured by Zarlink Semiconductor.

Programmable FIR FIlter Advance Information

DS4548 ISSUE 4.0 August 1998

The VP16256 contains sixteen multiplier

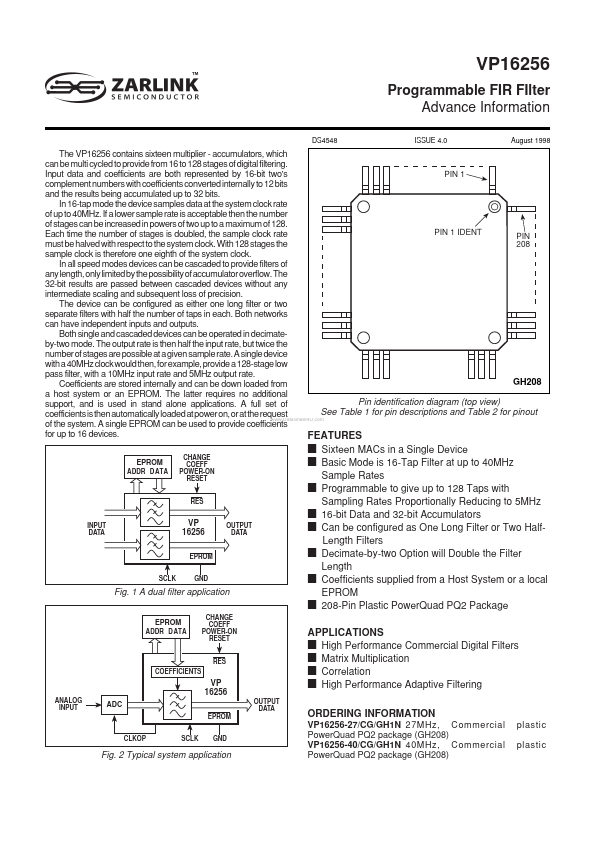

- accumulators, which can be multi cycled to provide from 16 to 128 stages of digital filtering. Input data and coefficients are both represented by 16-bit two’s PIN 1 plement numbers with coefficients converted internally to 12 bits and the results being accumulated up to 32 bits. In 16-tap mode the device samples data at the system clock rate of up to 40MHz. If a lower sample rate is acceptable then the number of stages can be increased in powers of two up to a maximum of 128. PIN 1 IDENT Each time the number of stages is doubled, the sample clock rate PIN must be...