ZL30111

Overview

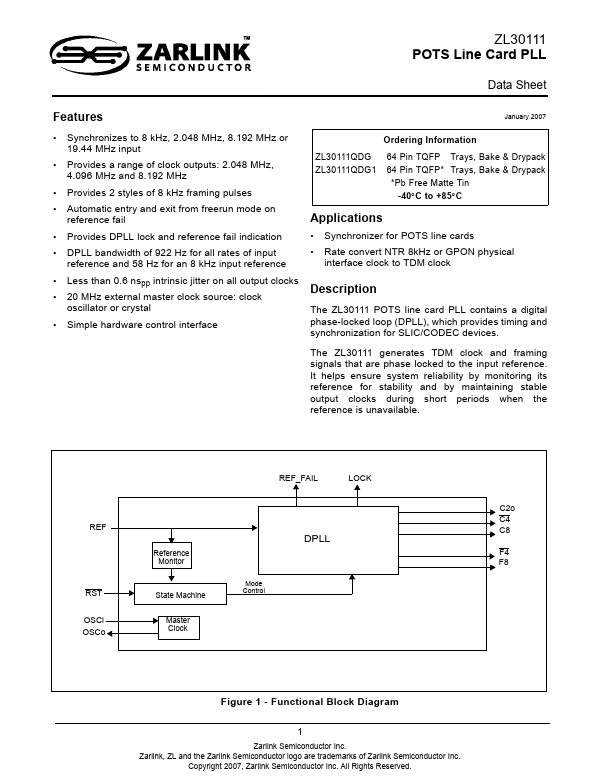

The ZL30111 POTS line card PLL contains a digital phase-locked loop (DPLL), which provides timing and synchronization for SLIC/CODEC devices. The ZL30111 generates TDM clock and framing signals that are phase locked to the input reference.

- Synchronizes to 8 kHz, 2.048 MHz, 8.192 MHz or 19.44 MHz input Provides a range of clock outputs: 2.048 MHz, 4.096 MHz and 8.192 MHz Provides 2 styles of 8 kHz framing pulses Automatic entry and exit from freerun mode on reference fail Provides DPLL lock and reference fail indication DPLL bandwidth of 922 Hz for all rates of input reference and 58 Hz for an 8 kHz input reference Less than 0.6 nspp intrinsic jitter on all output clocks 20 MHz external master clock source: clock oscillator or crystal Simple hardware control interface