54ACT11109

54ACT11109 is DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS manufactured by Texas Instruments.

54ACT11109, 74ACT11109 DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS

WITH CLEAR AND PRESET

SCAS451

- FEBRUARY 1987

- REVISED APRIL 1993

- Inputs Are TTL-Voltage patible

- Flow-Through Architecture Optimizes

PCB Layout

- Center-Pin VCC and GND Configurations

Minimize High-Speed Switching Noise

- EPIC™ (Enhanced-Performance Implanted

CMOS) 1-µm Process

- 500-m A Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic

Small-Outline Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs description

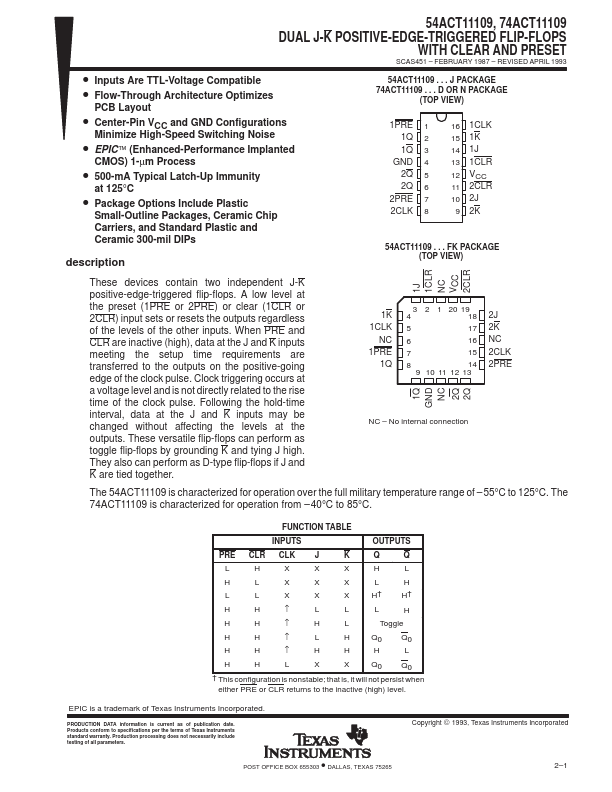

54ACT11109 . . . J PACKAGE 74ACT11109 . . . D OR N PACKAGE

(TOP VIEW)

1PRE 1Q 1Q

GND 2Q 2Q

2PRE 2CLK

1 2 3 4 5 6 7 8

16 1CLK 15 1K 14 1J 13 1CLR 12 VCC 11 2CLR 10 2J 9 2K

54ACT11109 . . . FK PACKAGE (TOP VIEW)

1J 1CLR NC VCC 2CLR

These devices contain two independent J-K positive-edge-triggered flip-flops. A low level at the preset (1PRE or 2PRE) or clear (1CLR or 2CLR) input sets or resets the outputs regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs meeting the setup time requirements are transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold-time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. These versatile flip-flops can perform as toggle flip-flops by grounding K and tying J high. They also can perform as D-type flip-flops if J and K are tied together.

1K 1CLK

NC 1PRE

1Q

3 2 1 20 19 4 18 5 17 6 16 7 15 8 14

9 10 11 12...