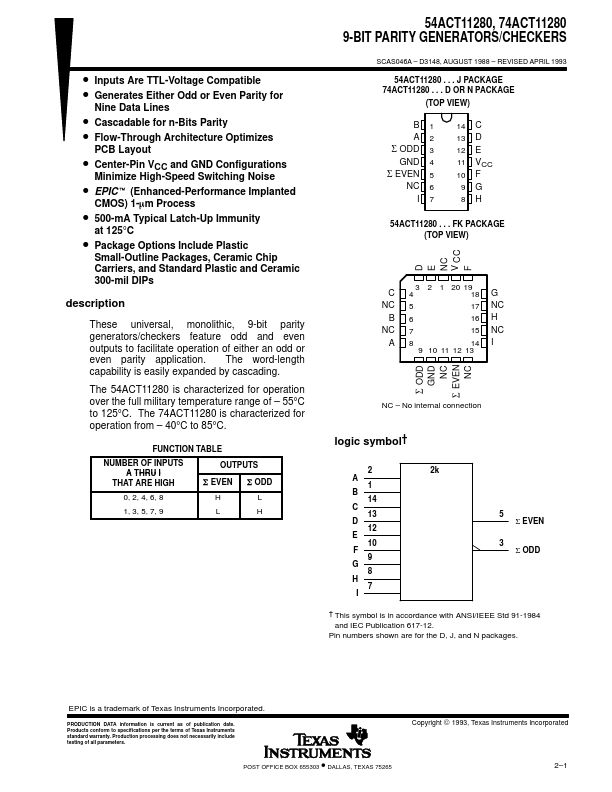

| Part | 54ACT11280 |

|---|---|

| Description | 9-BIT PARITY GENERATORS/CHECKERS |

| Manufacturer | Texas Instruments |

| Size | 98.17 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS280 | Hitachi Semiconductor | 9-bit Odd/Even Parity Generators/Checkers |

| 74LS280 | Hitachi Semiconductor | 9-bit Odd/Even Parity Generators/Checkers |

| SN54180 | Texas Instruments | 9-Bit Odd/Even Parity Generators/Checkers |