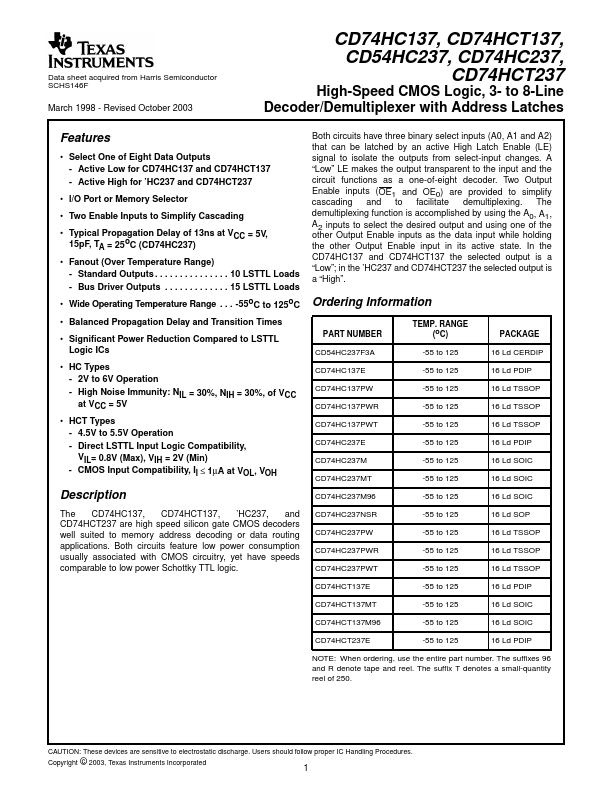

54HC237

Features

- Select One of Eight Data Outputs

- Active Low for CD74HC137 and CD74HCT137

- Active High for ’HC237 and CD74HCT237

- l/O Port or Memory Selector

- Two Enable Inputs to Simplify Cascading

- Typical Propagation Delay of 13ns 15p F, TA = 25o C (CD74HC237) at

=

5V,

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . -55o C to 125o C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction pared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30%, of VCC at VCC = 5V

- HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic patibility, VIL= 0.8V (Max), VIH = 2V (Min)

- CMOS Input patibility, Il ≤ 1µA at VOL, VOH

Description

Both circuits have three binary select inputs (A0, A1 and A2) that can be latched by an active High Latch Enable (LE) signal...