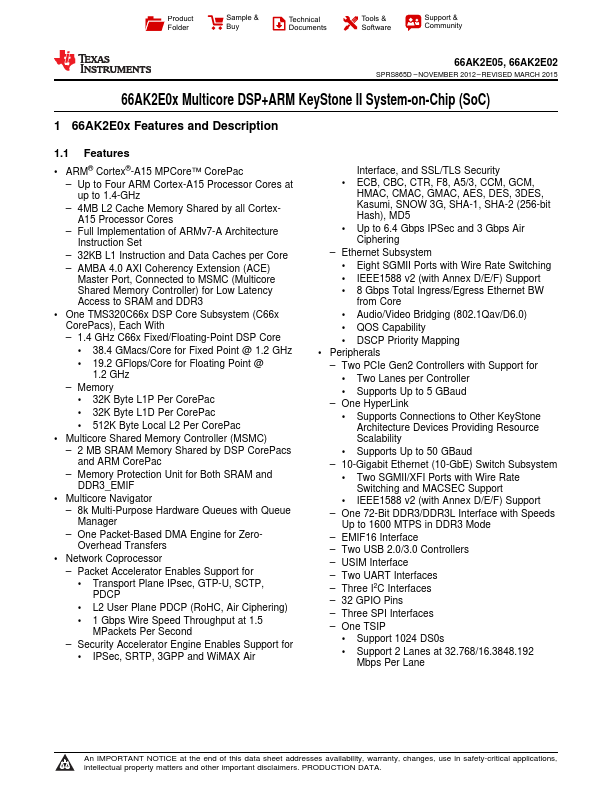

66AK2E02

Key Features

- 1 Features 1

- ARM® Cortex®-A15 MPCore™ CorePac - Up to Four ARM Cortex-A15 Processor Cores at up to 1.4-GHz - 4MB L2 Cache Memory Shared by all CortexA15 Processor Cores - Full Implementation of ARMv7-A Architecture Instruction Set - 32KB L1 Instruction and Data Caches per Core - AMBA 4.0 AXI Coherency Extension (ACE) Master Port, Connected to MSMC (Multicore Shared Memory Controller) for Low Latency Access to SRAM and DDR3

- One TMS320C66x DSP Core Subsystem (C66x CorePacs), Each With - 1.4 GHz C66x Fixed/Floating-Point DSP Core

- 38.4 GMacs/Core for Fixed Point @ 1.2 GHz

- 19.2 GFlops/Core for Floating Point @ 1.2 GHz - Memory

- 32K Byte L1P Per CorePac

- 32K Byte L1D Per CorePac

- 512K Byte Local L2 Per CorePac

- Multicore Shared Memory Controller (MSMC) - 2 MB SRAM Memory Shared by DSP CorePacs and ARM CorePac - Memory Protection Unit for Both SRAM and DDR3_EMIF

- Multicore Navigator - 8k Multi-Purpose Hardware Queues with Queue Manager - One Packet-Based DMA Engine for ZeroOverhead Transfers