Datasheet Summary

- Generates Either Odd or Even Parity for

Nine Data Lines

- Cascadable for n-Bits Parity

- Direct Bus Connection for Parity

Generation or for Checking by Using the

Parity I/O Port

- Flow-Through Architecture Optimizes

PCB Layout

- Center-Pin VCC and GND Configurations

Minimize High-Speed Switching Noise t- EPIC (Enhanced-Performance Implanted CMOS) 1-mm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic

Small-Outline Packages and Standard

Plastic 300-mil DIPs

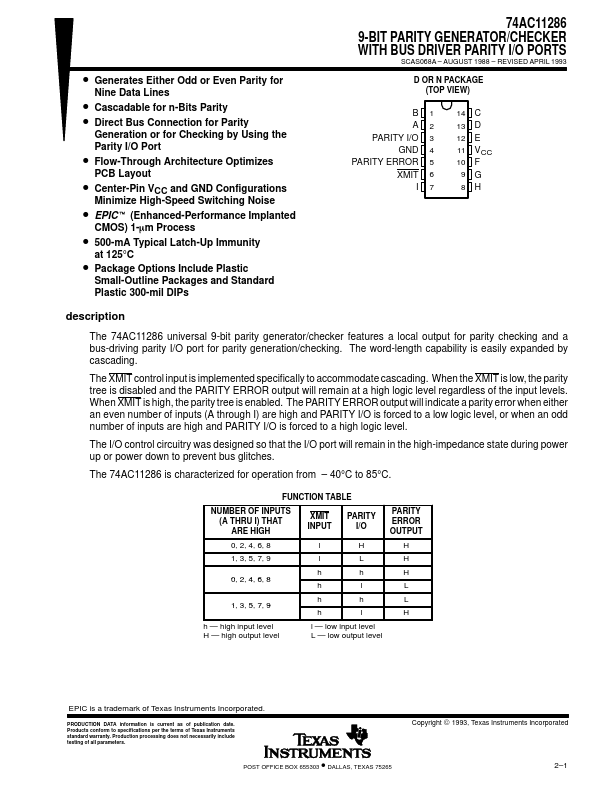

74AC11286 9-BIT PARITY GENERATOR/CHECKER WITH BUS DRIVER PARITY I/O PORTS

SCAS068A

- AUGUST 1988

- REVISED APRIL 1993

D OR N PACKAGE (TOP VIEW)

B A PARITY I/O GND PARITY ERROR XMIT I

1 2 3 4 5 6...