74HCT74

Features

- Operating voltage range of 4.5 V to 5.5 V

- Outputs can drive up to 10 LSTTL loads

- Low power consumption, 40-μA max ICC

- Typical tpd = 17 ns

- ±4-m A output drive at 5 V

- Low input current of 1 μA max

- Inputs are TTL-voltage patible

2 Description

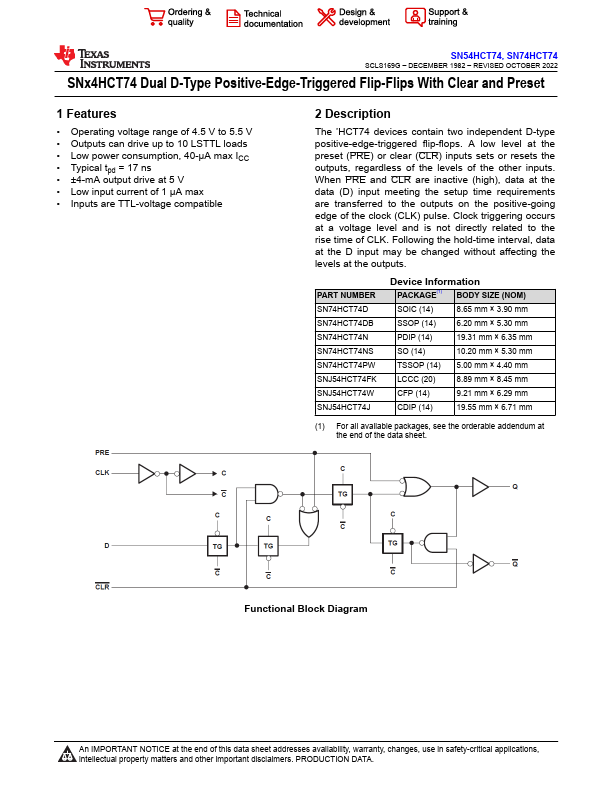

The ’HCT74 devices contain two independent D-type positive-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements are transferred to the outputs on the positive-going edge of the clock (CLK) pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of CLK. Following the hold-time interval, data at the D input may be changed without affecting the levels at the outputs.

PART NUMBER SN74HCT74D SN74HCT74DB SN74HCT74N SN74HCT74NS SN74HCT74PW SNJ54HCT74FK SNJ54HCT74W SNJ54HCT74J

Device...