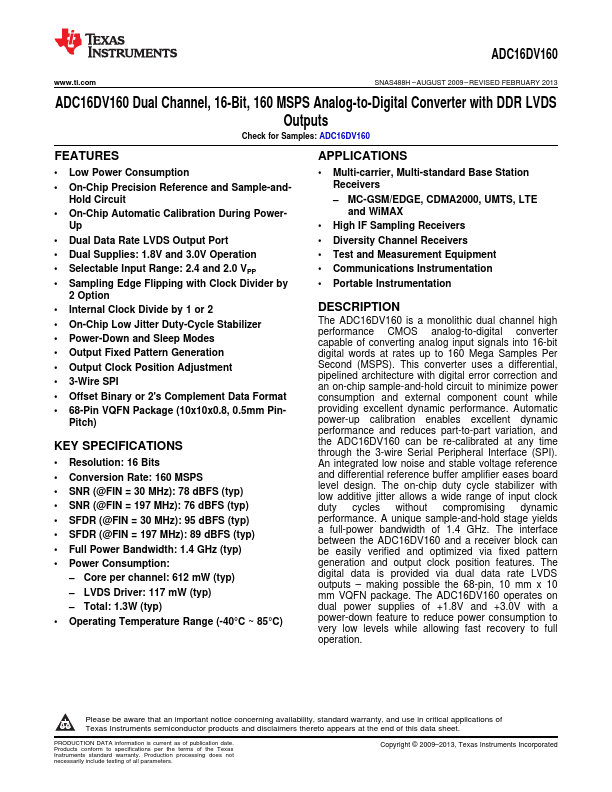

ADC16DV160

FEATURES

- Low Power Consumption

- On-Chip Precision Reference and Sample-and-

Hold Circuit

- On-Chip Automatic Calibration During Power-

Up

- Dual Data Rate LVDS Output Port

- Dual Supplies: 1.8V and 3.0V Operation

- Selectable Input Range: 2.4 and 2.0 VPP

- Sampling Edge Flipping with Clock Divider by

2 Option

- Internal Clock Divide by 1 or 2

- On-Chip Low Jitter Duty-Cycle Stabilizer

- Power-Down and Sleep Modes

- Output Fixed Pattern Generation

- Output Clock Position Adjustment

- 3-Wire SPI

- Offset Binary or 2's plement Data Format

- 68-Pin VQFN Package (10x10x0.8, 0.5mm Pin-

Pitch)

KEY SPECIFICATIONS

- Resolution: 16 Bits

- Conversion Rate: 160 MSPS

- SNR (@FIN = 30 MHz): 78 d BFS (typ)

- SNR (@FIN = 197 MHz): 76 d BFS (typ)

- SFDR (@FIN = 30 MHz): 95 d BFS (typ)

- SFDR (@FIN = 197 MHz): 89 d BFS (typ)

- Full Power Bandwidth: 1.4 GHz (typ)

- Power Consumption:

- Core per channel: 612 m W (typ)

- LVDS Driver: 117 m W (typ)

- Total: 1.3W (typ)

- Operating Temperature Range (-40°C ~...