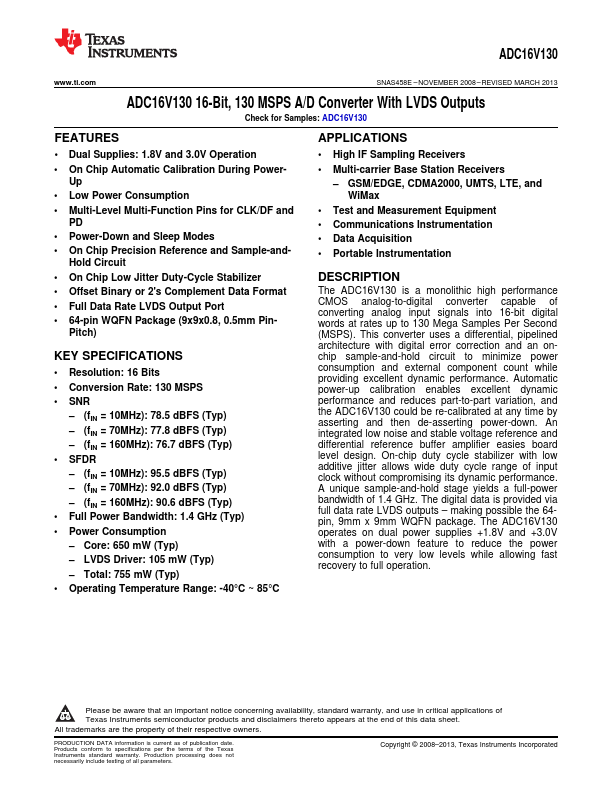

ADC16V130

FEATURES

- 2 Dual Supplies: 1.8V and 3.0V Operation

- On Chip Automatic Calibration During Power-

Up

- Low Power Consumption

- Multi-Level Multi-Function Pins for CLK/DF and

- Power-Down and Sleep Modes

- On Chip Precision Reference and Sample-and-

Hold Circuit

- On Chip Low Jitter Duty-Cycle Stabilizer

- Offset Binary or 2's plement Data Format

- Full Data Rate LVDS Output Port

- 64-pin WQFN Package (9x9x0.8, 0.5mm Pin-

Pitch)

KEY SPECIFICATIONS

- Resolution: 16 Bits

- Conversion Rate: 130 MSPS

- SNR

- (f IN = 10MHz): 78.5 d BFS (Typ)

- (f IN = 70MHz): 77.8 d BFS (Typ)

- (f IN = 160MHz): 76.7 d BFS (Typ)

- SFDR

- (f IN = 10MHz): 95.5 d BFS (Typ)

- (f IN = 70MHz): 92.0 d BFS (Typ)

- (f IN = 160MHz): 90.6 d BFS (Typ)

- Full Power Bandwidth: 1.4 GHz (Typ)

- Power Consumption

- Core: 650 m W (Typ)

- LVDS Driver: 105 m W (Typ)

- Total: 755 m W (Typ)

- Operating Temperature Range: -40°C ~ 85°C

APPLICATIONS

- High IF Sampling Receivers

- Multi-carrier Base Station Receivers

- GSM/EDGE, CDMA2000,...