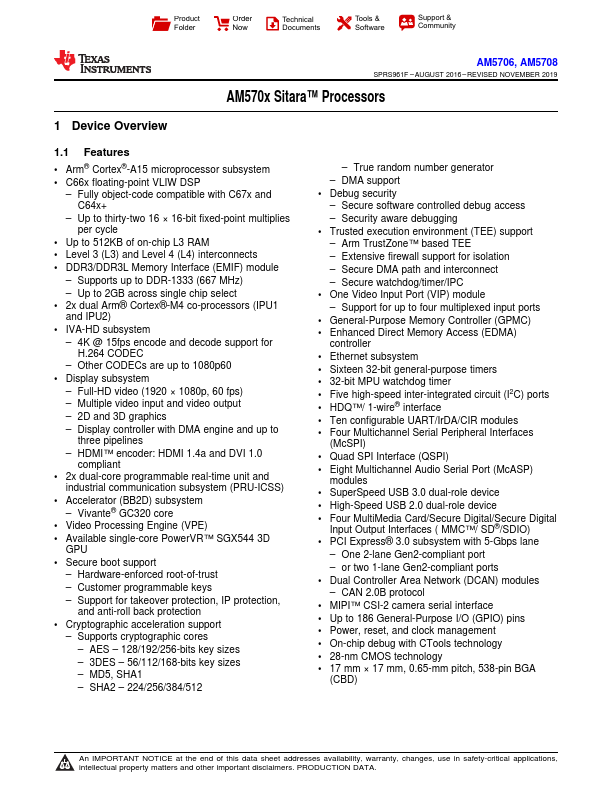

AM5706

Overview

- Arm® Cortex®-A15 microprocessor subsystem

- C66x floating-point VLIW DSP - Fully object-code compatible with C67x and C64x+ - Up to thirty-two 16 × 16-bit fixed-point multiplies per cycle

- Up to 512KB of on-chip L3 RAM

- Level 3 (L3) and Level 4 (L4) interconnects

- DDR3/DDR3L Memory Interface (EMIF) module - Supports up to DDR-1333 (667 MHz) - Up to 2GB across single chip select

- 2x dual Arm® Cortex®-M4 co-processors (IPU1 and IPU2)

- IVA-HD subsystem - 4K @ 15fps encode and decode support for H.264 CODEC - Other CODECs are up to 1080p60

- Display subsystem - Full-HD video (1920 × 1080p, 60 fps) - Multiple video input and video output - 2D and 3D graphics - Display controller with DMA engine and up to three pipelines - HDMI™ encoder: HDMI 1.4a and DVI 1.0 compliant

- 2x dual-core programmable real-time unit and industrial communication subsystem (PRU-ICSS)

- Accelerator (BB2D) subsystem - Vivante® GC320 core