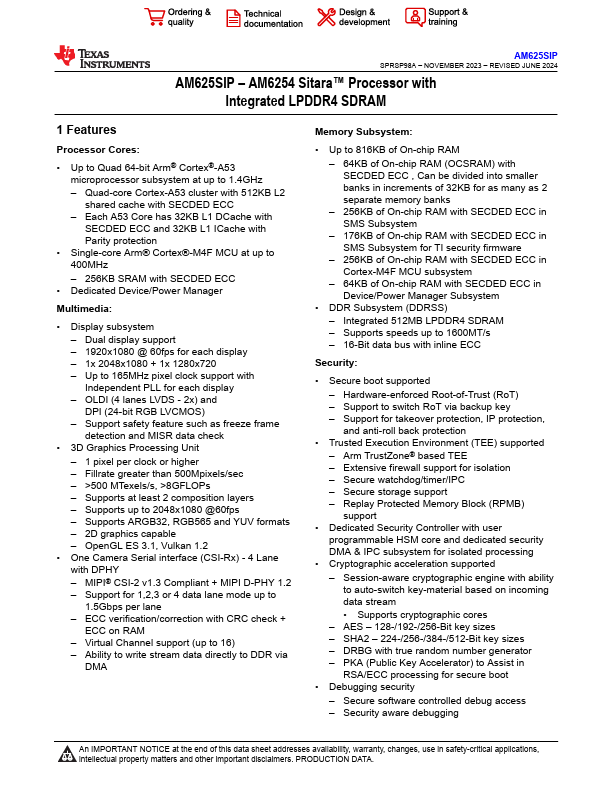

AM625SIP Overview

Key Features

- Single-core Arm® Cortex®-M4F MCU at up to 400MHz – 256KB SRAM with SECDED ECC

- Dedicated Device/Power Manager Multimedia

- 2x) and DPI (24-bit RGB LVCMOS) – Support safety feature such as freeze frame detection and MISR data check

- One Camera Serial interface (CSI-Rx)

- Ability to write stream data directly to DDR via DMA Memory Subsystem